- 談及嵌入式設備,安全性一直是人們關注的一大話題。然而目前為止,人們的注意力都放在了錯誤的方向上。不安全的網絡邊緣計算和物聯網設備已經證明,最薄弱(且經常被忽視)的環節往往導致重大的安全漏洞。慶幸的是,設計師現在可以采用一些重要的新方案確保將硬件可信根、集成加密、固件彈性等關鍵功能融入到各種互連設備的設計中。秘訣是什么?FPGA。具體而言,全新低功耗FPGA解決方案,如萊迪思MachXO5D-NX?系列芯片,搭配萊迪思Propel?和萊迪思Sentry?軟件解決方案,可以幫助設備和系統設計人員以經濟高效、低

- 關鍵字:

FPGA 嵌入式設備安全 萊迪思

- 本系列文章從數字芯片設計項目技術總監的角度出發,介紹了如何將芯片的產品定義與設計和驗證規劃進行結合,詳細講述了在FPGA上使用IP核來開發ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC IP來在FPGA上開發原型驗證系統設計時需要考量的因素。在上篇文章中,我們分享了第二到第四主題,介紹了使用FPGA進行原型設計時需要立即想到哪些基本概念、在將專為ASIC技術而設計的I

- 關鍵字:

ASIC IP FPGA SmartDV

- 引言隨著嵌入式系統的不斷發展,設計師面臨著越來越多的挑戰。功能性和連接性增加了集成的復雜性,尤其是在設計系統級芯片(SoC)時,通常很難提供最佳的邏輯架構來管理系統。本文將探討嵌入式FPGA(eFPGA)的結構,并探討如何在保持最大靈活性的同時,實現硅資源的最佳優化。高級SoC設計取代板級系統我們正進入一個將許多傳統PCB上的IC合并到單一單片IC或芯片組作為SoC的時代。如果IC設計團隊未能加入正確的功能,或者在設計部分發現了漏洞,他們可能會錯失市場機會或時間節點。傳統上,FPGA常用于原型設計、在PC

- 關鍵字:

FPGA

- 現場可編程門陣列(FPGA)在當今的眾多技術中發揮著重要作用。從航空航天和國防到消費電子產品,再到關鍵基礎設施和汽車行業,FPGA在我們生活中不斷普及。與此同時對FPGA器件的威脅也在不斷增長。想要開發在FPGA上運行(固件)的IP需要花費大量資源,受這些FPGA保護的技術也是如此。這使得FPGA成為IP盜竊或破壞的潛在目標。防止IP盜竊、客戶數據泄露和系統整體完整性所需的安全功能已經不可或缺。它們是許多FPGA應用的基礎,在某些地區有相應法律要求(例如,歐盟的GDPR、美國的HIPAA、英國的2018年

- 關鍵字:

萊迪思 Avant-X FPGA

- 設計需求:硬十開發的一塊基于安路EG4X20BG256的FPGA板卡。該系統應用于一個USB傳輸,可以進行多通道ADC數據采集的項目。整體框圖如下:實物如下:1、Buck控制器選型電源框圖制作過程,可以參考前期文檔:硬件總體設計之 “專題分析”我們可以看到在電源樹中,分別需要實現:5V→3.3V@2A5V→1.2V@2A5V→2.5V@2A此處我們選型的Buck電源控制器(集成Mosfet)是杰華特的JW5359從Datasheet我們可以看到:1、輸入電壓范圍滿足要求4.5V~18V2、輸出電流可以達到

- 關鍵字:

電路設計 FPGA BUCK電路

- 本系列文章從數字芯片設計項目技術總監的角度出發,介紹了如何將芯片的產品定義與設計和驗證規劃進行結合,詳細講述了在FPGA上使用IP核來開發ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC所用IP來在FPGA上開發原型驗證系統設計時需要考量的因素。在上篇文章中,我們介紹了將ASIC IP移植到FPGA原型平臺上的必要性,并對原型設計中各種考量因素進行了總體概述,分析開發A

- 關鍵字:

ASIC IP FPGA SmartDV

- 隨著人工智能(AI)技術的飛速發展,其應用邊界不斷拓寬,從簡單的圖像識別到復雜的自然語言處理,再到自動駕駛、智能制造等前沿領域,AI 正以前所未有的速度改變著我們的世界。在這場 AI 革命中,深度學習作為其核心驅動力,不斷推動著算法與模型的革新,同時也對計算資源提出了更為嚴苛的要求。誕生于 1985 年的 FPGA 雖然問世時間不長,但已經憑借「可編程」的獨特優勢,在百花齊放的芯片浪潮中奪得一席之地,成為 GPU 芯片的又一勁敵。FPGA 的特點FPGA 芯片是基于可編程器件(PAL、GAL、CPLD)發

- 關鍵字:

FPGA

- 本文從數字芯片設計項目技術總監的角度出發,介紹了如何將芯片的產品定義與設計和驗證規劃進行結合,詳細講述了在FPGA上使用IP核來開發ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC所用IP來在FPGA上開發原型驗證系統設計時需要考量的因素。本篇文章是SmartDV數字芯片設計經驗分享系列文章的第一篇,作為全球領先的驗證解決方案和設計IP提供商,SmartDV的產品研發及

- 關鍵字:

FPGA SmartDV

- 萊迪思半導體,低功耗可編程器件的領先供應商,今日宣布為其領先的小尺寸FPGA產品中再添一款邏輯優化的全新萊迪思Certus-NX? FPGA器件。新產品包括兩款新器件,即Certus-NX-28?和Certus-NX-09?,擁有多種封裝選項,可提供行業領先的低功耗、小尺寸和可靠性以及靈活的遷移選項。這些器件旨在加速廣泛的通信、計算、工業和汽車應用。萊迪思半導體產品營銷副總裁Dan Mansur表示:“萊迪思致力于在小型、低功耗FPGA領域持續創新,為我們的客戶提供優化的解決方案,滿足空間受限的應用需求,

- 關鍵字:

萊迪思 FPGA 小型FPGA

- 許多嵌入式系統的開發者都對使用基于FPGA的SoC系統感興趣,但是基于傳統HDL硬件描述語言的FPGA開發工具和復雜流程往往會令他們望而卻步。為了解決這一問題,萊迪思的Propel工具套件提供了基于圖形化設計方法的設計環境,用于創建,分析,編譯和調試基于FPGA的嵌入式系統,從而完成系統軟硬件設計。萊迪思的Propel工具套件由兩部分組成:Propel Builder提供圖形化的SoC系統和硬件設計,通過拖放方式,選擇處理器和相關的外設與IP,通過圖形化的方式進行配置和連接,從而完成系統層面的硬件設計;

- 關鍵字:

軟件設計工具 FPGA 萊迪思

- 萊迪思半導體,低功耗可編程器件的領先供應商,近日宣布推出兩款全新解決方案,進一步鞏固其在安全硬件和軟件領域的領先地位,幫助客戶應對系統安全領域日益嚴峻的挑戰。全新發布的萊迪思MachXO5D-NX?系列高級安全控制FPGA提供加密敏捷算法、集成閃存的硬件可信根功能以及故障安全(fail-safe)遠程現場更新功能,實現可靠和安全的產品生命周期管理。此外,萊迪思還推出了最新版本的Lattice Sentry?解決方案集合,其新功能為客戶提供可定制的、基于FPGA的平臺固件保護恢復(PFR)解決方案,且支持最

- 關鍵字:

萊迪思 安全控制 FPGA 加密敏捷性 硬件可信根

- 什么是PWMPWM(Pulse Width Modulation)簡稱脈寬調制,是利用微處理器的數字輸出來對模擬電路進行控制的一種非常有效的技術,廣泛應用在測量、通信、工控等方面。· PWM的頻率是指在1秒鐘內,信號從高電平到低電平再回到高電平的次數,也就是說一秒鐘PWM有多少個周期,單位Hz。· PWM的周期T=1/f,T是周期,f是頻率。如果頻率為50Hz ,也就是說一個周期是20ms,那么一秒鐘就有 50次PWM周期。· 占空比是一個脈沖周期內,高電平的時間與整個周期時間的比例,單位是% (0%-1

- 關鍵字:

PWM 電機 轉速控制

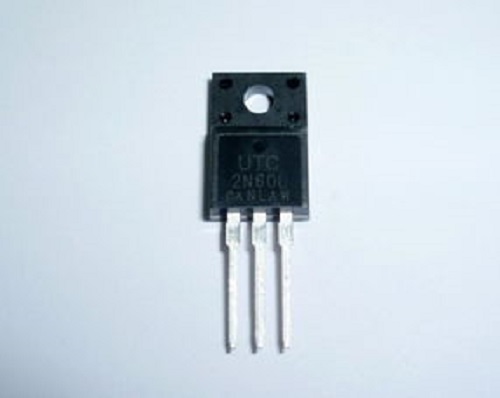

- 今天給大家分享的是:構建脈寬調制信號發生器脈寬調制(PWM)是一種利用數字信號精確控制模擬設備的技術。脈寬調制信號由用于模擬變化的模擬電壓的電子脈沖組成。脈寬調制信號通常用于控制伺服系統、LED和直流電機等模擬設備。一、脈寬調制的工作原理在脈沖寬度調制中,高頻電脈沖序列被發送到設備為其供電,脈沖可由驅動晶體管或功率MOS管生成。脈沖寬度調制信號出現在晶體管產生的高電壓和低電壓的周期中,信號從低電平循環到高電平所需的時間稱為周期持續時間。信號保持高電平的時間稱為脈沖寬度:脈沖寬度脈沖寬度與周期持續時間的比率

- 關鍵字:

脈寬調制信號發生器 PWM 伺服電機 直流電機

- 在我們傳統的LED燈中,一般調節光的亮度大多使用拔動開關等方式,在燈的生產過程中要手工一個一個地進行調節,比較浪費時間,而手工調試的結果,一致性很差。ST推出的ST25DV-PWM是經過NFC讀寫進行PWM控制調節LED燈的亮度,工廠生產既方便、省時而一致性俱佳,可大大提升生產效率,非常適合LED燈的應用。 這是一個基于NFC近場通信的技術應用,工作在13.56MHz頻率,讀寫距離可以在10-30cm,依賴天線的大小和設計。在目前的各類產品,NFC得到廣泛的應用,如我們家居的智能門鎖、手機等,我們可以很方

- 關鍵字:

NFC ST25DV-PWM 照明控制

- 摘要本文根據完整的基準測試,將Achronix Semiconductor公司推出的Speedster7t FPGA與GPU解決方案進行比較,在運行同一個Llama2 70B參數模型時,該項基于FPGA的解決方案實現了超越性的LLM推理處理。采用 FPGA 器件來加速LLM 性能,在運行 Llama2 70B 參數模型時,Speedster7t FPGA 如何與 GPU 解決方案相媲美?證據是令人信服的——Achronix Speedster7t FPGA通過提供計算能力、內存帶寬和卓越能效的最佳組合,在

- 關鍵字:

Achronix FPGA

fpga-pwm介紹

您好,目前還沒有人創建詞條fpga-pwm!

歡迎您創建該詞條,闡述對fpga-pwm的理解,并與今后在此搜索fpga-pwm的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473