fpga-pwm 文章 最新資訊

基于FPGA 的誤碼率測試儀的設(shè)計與實(shí)現(xiàn)

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: FPGA

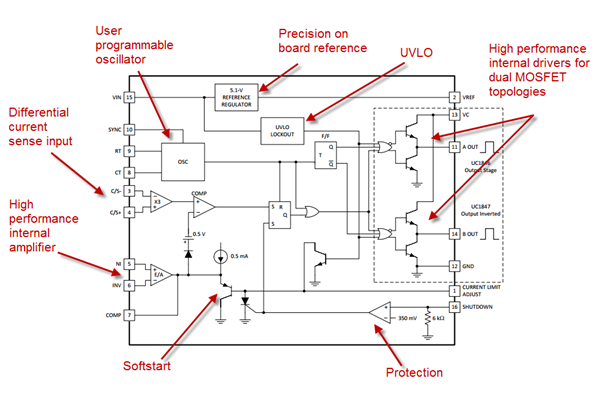

小型的簡單PWM降壓控制器可以代替高電流LDO

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: 安森美半導(dǎo)體 LDO PWM

基于FPGA的MPEG-2復(fù)用器中FIFO的一種設(shè)計方案

- 近幾年基于MPEC-2的DVB普通數(shù)字電視在美國、南美、亞洲、大洋洲和非洲通過衛(wèi)星進(jìn)行廣播。基于MPEG-2/DVB的多路節(jié)目復(fù)用器是數(shù)字電視傳輸系統(tǒng)的關(guān)鍵設(shè)備之一,因此,它的研發(fā)顯得尤為重要。 目前,復(fù)用器的設(shè)計方案主要基于DSP(數(shù)字信號處理器)的實(shí)現(xiàn)技術(shù),這種設(shè)計方法在理論上也能實(shí)現(xiàn)對傳送流的復(fù)用,考慮到實(shí)現(xiàn)復(fù)用器諸多高速、復(fù)雜的邏輯功能,同時,F(xiàn)PGA(現(xiàn)場可編程門陣列)理論上可以無限次地重新配置,這樣在一定程度上為系統(tǒng)的升級或局部功

- 關(guān)鍵字: FPGA MPEG-2

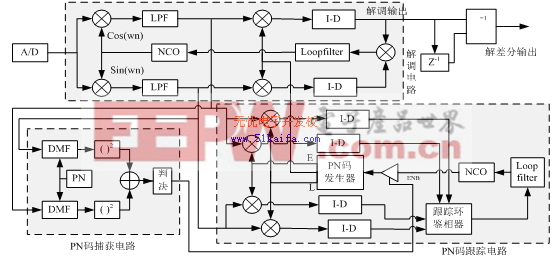

基于FPGA的偽碼測距電路的設(shè)計與實(shí)現(xiàn)

- 1 引 言 現(xiàn)場可編程門陣列(FPGA)用硬件電路完成算法的過程,一方面解決了系統(tǒng)的開銷問題,提供了提高系統(tǒng)整體性能的條件,另一方面,由于靜態(tài)RAM型的FPGA具備可重構(gòu)特性,這使得資源利用率得到顯著提高。FPGA既具有通用計算系統(tǒng)的靈活性,又有專用處理系統(tǒng)的性能,對實(shí)現(xiàn)高性能信號處理具有很高的應(yīng)用價值,而且可重構(gòu)的特性使其可以根據(jù)算法來調(diào)整相應(yīng)的通信結(jié)構(gòu)和數(shù)據(jù)字長。FPGA以其高度的靈活性與硬件的高密度性在通信信號處理中得到了廣泛的應(yīng)用。 在對Xili

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) FPGA 偽碼測距

FPGA創(chuàng)新中心落戶無錫國家集成電路設(shè)計基地

- 可編程解決方案領(lǐng)導(dǎo)廠商賽靈思公司(Xilinx)與無錫國家高新技術(shù)產(chǎn)業(yè)開發(fā)區(qū)管理委員會今天共同宣布成立無錫國家集成電路設(shè)計基地FPGA(現(xiàn)場可編程門陣列)創(chuàng)新中心,并隆重舉行賽靈思正式授權(quán)“無錫國家集成電路設(shè)計基地—賽靈思聯(lián)合實(shí)驗(yàn)室”揭牌儀式。無錫新區(qū)管委會副主任朱曉紅以及賽靈思公司研究實(shí)驗(yàn)室高級總監(jiān)、全球大學(xué)計劃負(fù)責(zé)人Patrick Lysaght等出席了成立大會并為聯(lián)合實(shí)驗(yàn)室揭牌。 作為國家級的集成電路設(shè)計基地,新的FPGA創(chuàng)新中心的成立以及聯(lián)合實(shí)驗(yàn)室的打造,意味著可編程設(shè)計在電子設(shè)計領(lǐng)域的

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) FPGA 無錫 集成電路設(shè)計 嵌入式

FPGA:22年從配角到主角

- 任何一個從事后看來很成功的新事物從誕生到發(fā)展壯大都不可避免地經(jīng)歷過艱難的歷程并可能成為被研究的案例,F(xiàn)PGA也不例外。1985年,當(dāng)全球首款FPGA產(chǎn)品——XC2064誕生時,注定要使用大量芯片的PC機(jī)剛剛走出硅谷的實(shí)驗(yàn)室進(jìn)入商業(yè)市場,因特網(wǎng)只是科學(xué)家和政府機(jī)構(gòu)通信的神秘鏈路,無線電話笨重得像磚頭,日后大紅大紫的Bill Gates正在為生計而奮斗,創(chuàng)新的可編程產(chǎn)品似乎并沒有什么用武之地。 事實(shí)也的確如此。最初,F(xiàn)PGA只是用于膠合邏輯,從膠合邏輯到算法

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) FPGA 嵌入式

利用FPGA實(shí)現(xiàn)UART的設(shè)計

- 引 言 隨著計算機(jī)技術(shù)的發(fā)展和廣泛應(yīng)用,尤其是在工業(yè)控制領(lǐng)域的應(yīng)用越來越廣泛,計算機(jī)通信顯的尤為重要。串行通信雖然使設(shè)備之間的連線大為減少,但隨之帶來串/并轉(zhuǎn)換和位計數(shù)等問題,這使串行通信技術(shù)比并行通信技術(shù)更為復(fù)雜。串/并轉(zhuǎn)換可用軟件實(shí)現(xiàn),也可用硬件實(shí)現(xiàn)。用軟件實(shí)現(xiàn)串行傳送大多采用循環(huán)移位指令將一個字節(jié)由高位到低位(或低位到高位)一位一位依次傳送,這種方法雖然簡單但速度慢,而且大量占用CPU的時間,影響系統(tǒng)的性能。更為方便的實(shí)現(xiàn)方法是用硬件,目前微處理器串行接口常用的LSI 芯片是UART(通用異

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) UART FPGA

基于FPGA的八位RISC CPU的設(shè)計

- 1 引 言 隨著數(shù)字通信和工業(yè)控制領(lǐng)域的高速發(fā)展,要求專用集成電路(ASIC)的功能越來越強(qiáng),功耗越來越低,生產(chǎn)周期越來越短,這些都對芯片設(shè)計提出了巨大的挑戰(zhàn),傳統(tǒng)的芯片設(shè)計方法已經(jīng)不能適應(yīng)復(fù)雜的應(yīng)用需求了。SoC(System on a Chip)以其高集成度,低功耗等優(yōu)點(diǎn)越來越受歡迎。開發(fā)人員不必從單個邏輯門開始去設(shè)計ASIC,而是應(yīng)用己有IC芯片的功能模塊,稱為核(core),或知識產(chǎn)權(quán)(IP)宏單元進(jìn)行快速設(shè)計,效率大為提高。CPU 的IP

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) RISC CPU FPGA

Altera首次實(shí)現(xiàn)了對關(guān)鍵工業(yè)以太網(wǎng)協(xié)議的FPGA IP支持

- Altera公司日前宣布為工業(yè)自動化應(yīng)用中的以太網(wǎng)通信協(xié)議提供FPGA支持,這些應(yīng)用包括ProfiNet、Ethernet/IP、Modbus-IDA、EtherCAT、SERCOS III接口和Ethernet Powerlink等。這些關(guān)鍵通信協(xié)議的知識產(chǎn)權(quán)(IP)內(nèi)核現(xiàn)在可以在Altera低成本Cyclone®系列FPGA中實(shí)現(xiàn)。 設(shè)計人員利用工業(yè)以太網(wǎng)IP內(nèi)核可以在一塊電路板上實(shí)現(xiàn)任何標(biāo)準(zhǔn),這不但減小了外形尺寸,而且節(jié)省了時間。系統(tǒng)OEM能夠以高性價比方式在其自動化產(chǎn)品中增加工業(yè)

- 關(guān)鍵字: 工業(yè)以太網(wǎng) FPGA IP 嵌入式 工業(yè)控制

基于FPGA的智能控制器設(shè)計及測試方法研究

- 摘要:通過模糊自整定PID控制器的設(shè)計,本文提出了一種基于VHDL描述、DSP Builder和Modelsim混合仿真、FPGA實(shí)現(xiàn)的智能控制器設(shè)計及測試新方法。首先,通過MATLAB仿真,得出智能控制器的結(jié)構(gòu)和參數(shù)。然后,基于VHDL進(jìn)行智能控制器的數(shù)字化實(shí)現(xiàn)及其開環(huán)測試。在此基礎(chǔ)上,通過分析一般智能控制器的測試特點(diǎn),采用DSP Builder構(gòu)建閉環(huán)測試系統(tǒng),Modelsim運(yùn)行DSP Builder生成文件來驗(yàn)證QuartusII中所做VHDL設(shè)計的測試方法。實(shí)驗(yàn)表明,該測試方法能有效模擬控制器的

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) FPGA 智能控制器 嵌入式

Altera宣布其Cyclone III FPGA提供對EtherCAT IP支持

- Altera公司日前宣布為EtherCAT技術(shù)協(xié)會的EtherCAT協(xié)議提供知識產(chǎn)權(quán)(IP)支持。此前IP是針對Cyclone® II器件,現(xiàn)在將針對Altera新的低成本、低功耗Cyclone III FPGA。 EtherCAT技術(shù)協(xié)會執(zhí)行總監(jiān)Martin Rostan說:“在競爭非常激烈的工廠自動化設(shè)備市場上,企業(yè)正在尋找能夠迅速突出產(chǎn)品優(yōu)勢的新功能和特性。Cyclone III FPGA實(shí)現(xiàn)對EtherCAT的支持,使設(shè)計人員能夠以高性價比方式,輕松加入實(shí)時以太網(wǎng)功能。”

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) Altera FPGA Cyclone EtherCAT IP 嵌入式

利用FPGA實(shí)現(xiàn)UART的設(shè)計

- 引 言 隨著計算機(jī)技術(shù)的發(fā)展和廣泛應(yīng)用,尤其是在工業(yè)控制領(lǐng)域的應(yīng)用越來越廣泛,計算機(jī)通信顯的尤為重要。串行通信雖然使設(shè)備之間的連線大為減少,但隨之帶來串/并轉(zhuǎn)換和位計數(shù)等問題,這使串行通信技術(shù)比并行通信技術(shù)更為復(fù)雜。串/并轉(zhuǎn)換可用軟件實(shí)現(xiàn),也可用硬件實(shí)現(xiàn)。用軟件實(shí)現(xiàn)串行傳送大多采用循環(huán)移位指令將一個字節(jié)由高位到低位(或低位到高位)一位一位依次傳送,這種方法雖然簡單但速度慢,而且大量占用CPU的時間,影響系統(tǒng)的性能。更為方便的實(shí)現(xiàn)方法是用硬件,目前微處理器串行接口常用的LSI 芯片是UART(通用異

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) FPGA UART 嵌入式

fpga-pwm介紹

您好,目前還沒有人創(chuàng)建詞條fpga-pwm!

歡迎您創(chuàng)建該詞條,闡述對fpga-pwm的理解,并與今后在此搜索fpga-pwm的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga-pwm的理解,并與今后在此搜索fpga-pwm的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司