EEPW首頁(yè) >>

主題列表 >>

fpga+dsp

fpga+dsp 文章 最新資訊

DSP數(shù)字信號(hào)處理器在科里奧利質(zhì)量流量計(jì)上的應(yīng)用

- 艾默生過程管理旗下的高準(zhǔn)(Micro Motion)公司新近推出MVD多參數(shù)數(shù)字變送器,它以DSP數(shù)字信號(hào)處理技術(shù)的使用為特點(diǎn),顯示了高準(zhǔn)公司在科里奧利質(zhì)量流量測(cè)量技術(shù)上的雄厚實(shí)力。 高準(zhǔn) MVD多參數(shù)數(shù)字技術(shù)提供了一個(gè)模式化的結(jié)構(gòu)來重新定義傳感器和變送器,并使流量計(jì)工作得更靈巧。DSP數(shù)字信號(hào)處理器的核心處理器與傳感器安裝在一起,把來自科里奧利傳感器中的模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),并產(chǎn)生一個(gè)正比于質(zhì)量流量的電子信號(hào)。 1000系列和2000系列兩種變送器可與核心處理器之間通過普通的4線電纜相

- 關(guān)鍵字: DSP 科里奧利質(zhì)量流量測(cè)量 微處理器 科里奧利傳感器 ADC 傅立葉分析

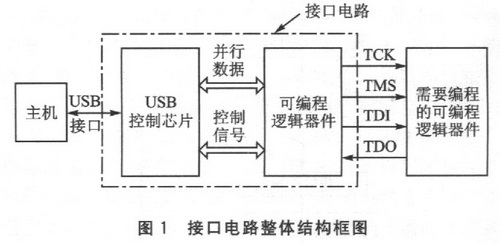

基于CPLD的USB下載電纜設(shè)計(jì)

- 引 言 隨著片上系統(tǒng)(SoC,System on Chip)時(shí)代的到來,包括復(fù)雜可編程邏輯器件(CPLD,Complex ProgrammableLogic Devi(e)和現(xiàn)場(chǎng)可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)的可編程邏輯器件(具有在系統(tǒng)可再編程的獨(dú)特優(yōu)點(diǎn)),應(yīng)用越來越廣泛。這給用于可編程邏輯器件編程的下載電纜提出了更高的要求。 本文研究基于IEEEll49.1標(biāo)準(zhǔn)的USB下載接口電路的設(shè)計(jì)及實(shí)現(xiàn)。針對(duì)Altera公司的FPGA器件Cy-

- 關(guān)鍵字: CPLD USB FPGA 下載電纜 SoC

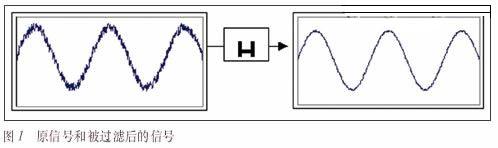

采用DSP、PLD和ASIC實(shí)現(xiàn)多速濾波器設(shè)計(jì)的比較

- 許多通信系統(tǒng)都要用到多速濾波器(multirate filter),多速濾波器是指輸出數(shù)據(jù)速率與輸入數(shù)據(jù)速率不相等的濾波器,常用于某個(gè)物理接口如數(shù)模轉(zhuǎn)換器(DAC)或模數(shù)轉(zhuǎn)換器(ADC)的接口處。

- 關(guān)鍵字: ASIC DSP PLD 濾波器設(shè)計(jì)

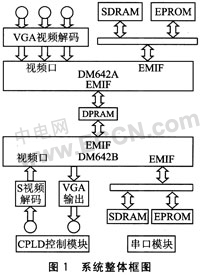

DM642平臺(tái)多路視頻處理系統(tǒng)的實(shí)時(shí)性分析

- 引 言 視頻合成技術(shù)是圖像處理方面的一個(gè)重要應(yīng)用,它將一個(gè)圖像的多個(gè)狀態(tài)或者多幅不同圖像進(jìn)行合成,來實(shí)現(xiàn)虛擬面板、圖像疊加、模擬場(chǎng)景、圖像優(yōu)化等效果。多路視頻合成顯示技術(shù)是將通過多個(gè)途徑(如攝像機(jī)、PC機(jī)、網(wǎng)絡(luò)等),采集而來的多路視頻信號(hào)進(jìn)行處理,并按照實(shí)際所需進(jìn)行顯示。 選擇適當(dāng)?shù)暮诵奶幚硇酒瑢?duì)數(shù)據(jù)量大、實(shí)時(shí)性高的視頻信號(hào)處理來說,是首要考慮的問題。美國(guó)TI公司推出的針對(duì)視頻和圖像解決方案的TMS320DM642型高性能數(shù)字媒體處理器,是TI公司C6000系列中一款基于DaVinci技

- 關(guān)鍵字: DSP DM642 視頻合成技術(shù) TI 數(shù)字媒體處理器

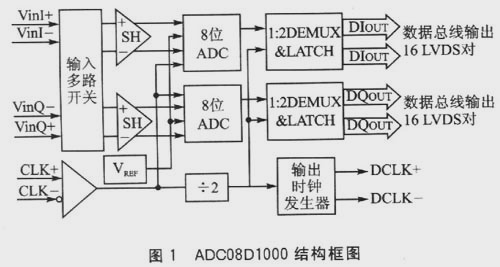

千兆高速采集系統(tǒng)的硬件電路設(shè)計(jì)

- 1 ADC08D1000的結(jié)構(gòu) ADC08D1000是NS(National Semiconductor,國(guó)家半導(dǎo)體)公司于2005年推出的雙通道低功耗的高速8位A/D轉(zhuǎn)換器,其最高單通道采樣頻率達(dá)l.3 GHz,全功率帶寬(FPBW)為1.7 GHz,在500 MHz標(biāo)準(zhǔn)信號(hào)輸入的情況下可以獲得7.4位的有效采樣位數(shù)。整個(gè)A/D轉(zhuǎn)換器用單電源1.9V供電,內(nèi)帶高質(zhì)量參考源和高性能采樣保持電路,每個(gè)通道均為差分輸入,采樣范圍可選為650 mV或870 mV(峰一峰值)。在高速數(shù)/模轉(zhuǎn)換系統(tǒng)中,有

- 關(guān)鍵字: 硬件電路 NS A/D轉(zhuǎn)換器 FPGA LVDS

基于TMS320F2812的DSP控制器設(shè)計(jì)及應(yīng)用

- 基于DSP芯片TMS320F2812的電機(jī)控制器設(shè)計(jì),描述了其引導(dǎo)加載ROM、AD轉(zhuǎn)換單元、傳感器接口、cpld等電機(jī)控制外設(shè)電路的技術(shù)關(guān)鍵。還簡(jiǎn)單介紹了其在調(diào)速系統(tǒng)中的應(yīng)用。

- 關(guān)鍵字: 設(shè)計(jì) 應(yīng)用 控制器 DSP TMS320F2812 基于

外形似集成電路的完整 DC/DC 解決方案為基于 FPGA 的系統(tǒng)帶來切實(shí)益處

- FPGA工藝尺寸的進(jìn)步和更加靈活的設(shè)計(jì)配置、以及基于FPGA的系統(tǒng)取得的進(jìn)步已經(jīng)使FPGA制造商充滿信心地進(jìn)入了以前由微處理器和ASIC供應(yīng)商壟斷的市場(chǎng)。最近,Xilinx的VirtexTM和Altera的Stratix產(chǎn)品系列分別推出了新器件,進(jìn)一步縮小了性能差距,再次提高了性能標(biāo)準(zhǔn)。盡管這些器件的通用和可配置性吸引了系統(tǒng)設(shè)計(jì)師,但是控制這些器件內(nèi)部工作方式的設(shè)計(jì)規(guī)則及其外部接口協(xié)議的復(fù)雜性導(dǎo)致需要廣泛的培訓(xùn)、基準(zhǔn)設(shè)計(jì)評(píng)估、設(shè)計(jì)仿真和驗(yàn)證。因此,F(xiàn)PGA供應(yīng)商提供了詳盡的硬件和固件支持,旨在幫助系統(tǒng)設(shè)計(jì)

- 關(guān)鍵字: DC/DC ,解決方案,F(xiàn)PGA

安富利電子元件部推出Virtex-5 FXT FPGA評(píng)估工具套件

- 安富利公司 (NYSE: AVT) 旗下安富利電子元件部宣布推出Xilinx® Virtex®-5 FXT FPGA 評(píng)估工具套件。該套件以Xilinx最新的Virtex-5 FXT 現(xiàn)場(chǎng)門陣列(FPGA)為基礎(chǔ),還包括了一塊評(píng)估板、ISE® Design Suite 10.1 WebPACK™ 設(shè)計(jì)工具、評(píng)估版Embedded Development Kit (EDK)軟件、電源并能獲得參考設(shè)計(jì)和設(shè)計(jì)指南等資料。此套件成本低廉,是意圖研究Virtex-5 FXT平

- 關(guān)鍵字: 安富利公司 安富利電子元件部 Xilinx FPGA 評(píng)估工具套件

基于定點(diǎn)DSP的MP3實(shí)時(shí)解碼器的設(shè)計(jì)與實(shí)現(xiàn)

- 本文簡(jiǎn)要介紹了MP3解碼原理,并詳細(xì)說明了MP3在FD216定點(diǎn)DSP上實(shí)現(xiàn)實(shí)時(shí)解碼的設(shè)計(jì)、開發(fā)流程。

- 關(guān)鍵字: 解碼器 設(shè)計(jì) 實(shí)現(xiàn) 實(shí)時(shí) MP3 定點(diǎn) DSP 基于

如何處理好嵌入式DSP設(shè)計(jì)中的功耗優(yōu)化

- 對(duì)基于數(shù)字信號(hào)處理器(DSP)的系統(tǒng)而言,優(yōu)化功耗是一項(xiàng)重要但往往難以實(shí)現(xiàn)的設(shè)計(jì)目標(biāo)。現(xiàn)在,基于DSP的設(shè)備常常把以往各自獨(dú)立的多個(gè)應(yīng)用結(jié)合起來,每一個(gè)應(yīng)用都可能有多個(gè)工作模式。要得到這樣一個(gè)設(shè)備的功率分布是非常困難的一件事,更遑論整個(gè)復(fù)雜的系統(tǒng)。設(shè)計(jì)人員需要獲知盡可能多的最佳信息,以及能夠幫助他們優(yōu)化特定應(yīng)用之功耗的技術(shù)和工具。

- 關(guān)鍵字: 功耗 優(yōu)化 設(shè)計(jì) DSP 處理 嵌入式 如何

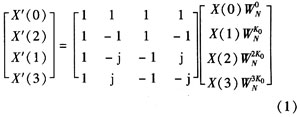

基于FPGA的高速流水線FFT算法實(shí)現(xiàn)

- 0 引言 有限長(zhǎng)序列的DFT(離散傅里葉變換)特點(diǎn)是能夠?qū)㈩l域的數(shù)據(jù)離散化成有限長(zhǎng)的序列。但由于DYT本身運(yùn)算量相當(dāng)大,限制了它的實(shí)際應(yīng)用。FFT(快速傅里葉變換)算法是作為DFT的快速算法提出,它將長(zhǎng)序列的DFT分解為短序列的DFT,大大減少了運(yùn)算量,使得DFT算法在頻譜分析、濾波器設(shè)計(jì)等領(lǐng)域得到了廣泛的應(yīng)用。 FPGA(現(xiàn)場(chǎng)可編程門陣列)是一種具有大規(guī)模可編程門陣列的器件,不僅具有專用集成電路(ASIC)快速的特點(diǎn),更具有很好的系統(tǒng)實(shí)現(xiàn)的靈活性。FPGA可通過開發(fā)工具實(shí)現(xiàn)在線編程。與C

- 關(guān)鍵字: FPGA FFT 集成電路 DFT

基于DSP的視頻采集系統(tǒng)設(shè)計(jì)

- 0 引言 數(shù)字圖象處理技術(shù)在電子通信與信息處理領(lǐng)域得到了廣泛的應(yīng)用,設(shè)計(jì)一種功能靈活、使用方便、便于嵌入到系統(tǒng)中的視頻信號(hào)采集電路具有重要的實(shí)用意義。 在研究基于DSP的視頻監(jiān)控系統(tǒng)時(shí),考慮到高速實(shí)時(shí)處理及實(shí)用化兩方面的具體要求,需要開發(fā)一種具有高速、高集成度等特點(diǎn)的視頻圖象信號(hào)采集系統(tǒng),為此系統(tǒng)采用專用視頻解碼芯片和復(fù)雜可編程邏輯器件(CPLD)構(gòu)成前端圖象采集部分。設(shè)計(jì)上采用專用視頻解碼芯片,以CPLD器件作為控制單元和外圍接口,以FIFO為緩存結(jié)構(gòu),能夠有效地實(shí)現(xiàn)視頻信號(hào)的采集與讀取

- 關(guān)鍵字: DSP 數(shù)據(jù)采集 視頻采集 CPLD 數(shù)字圖象處理

一種基于TMS320C55x DSP的UART通信設(shè)計(jì)

- 提出了一種直接利用DSP的MCBSP接口和DMA通道實(shí)現(xiàn)UART的方法,給出了使用C語(yǔ)言和CSL的編程方法。與傳統(tǒng)實(shí)現(xiàn)方法相比,具有實(shí)現(xiàn)成本低,硬件電路簡(jiǎn)單,移植性強(qiáng)等特點(diǎn),稍加修改可應(yīng)用于C5000和C6000各系列芯片中。

- 關(guān)鍵字: 通信 設(shè)計(jì) UART DSP TMS320C55x 基于

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司