fpga) 文章 最新資訊

基于FPGA的高速圖像采集系統(tǒng)設(shè)計

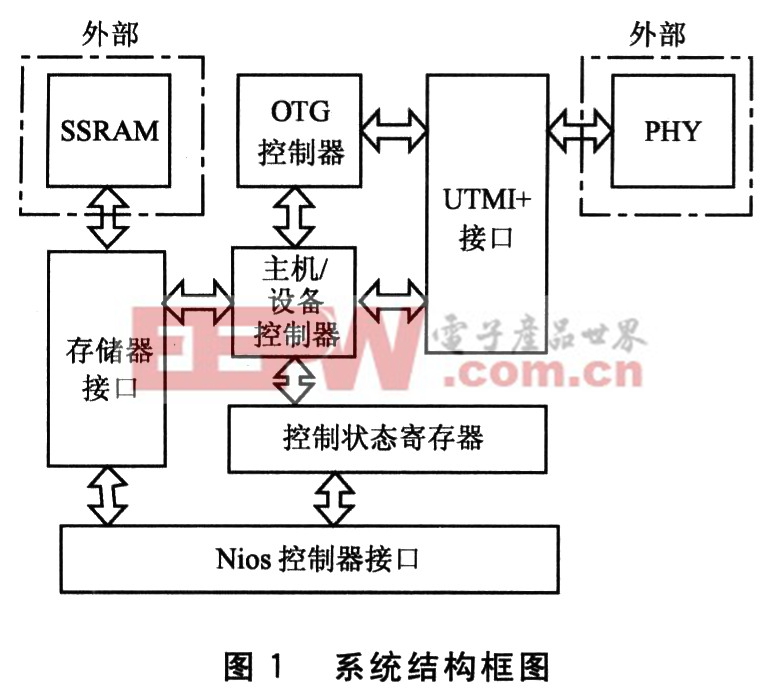

- 在高速圖像采集系統(tǒng)中,CPU時鐘資源、I/O端口資源、傳輸單元等都成為系統(tǒng)的瓶頸。本系統(tǒng)采用FPGA+RAM+USB的設(shè)計:FPGA硬件采樣模塊,有效降低采樣時延和CPU時鐘資源;獨特的RAM時序控制與讀寫控制分離設(shè)計,增加了模塊之間的獨立性,降低了控制的復雜度;USB設(shè)計在實現(xiàn)高速率數(shù)據(jù)傳輸?shù)耐瑫r又具有低成本、易安裝等優(yōu)點。

- 關(guān)鍵字: FPGA 高速圖像采集 系統(tǒng)設(shè)計

用FPGA實現(xiàn)數(shù)字電視條件接收系統(tǒng)

- 摘 要:根據(jù)數(shù)字電視條件接收系統(tǒng)的原理,提出一種ECM在 TS層加入、復接和條件接收相互獨立的CAS實現(xiàn)方法。ECM在TS層加入,對于TS層加擾來說,易于實現(xiàn)加擾和解擾同步;復接和條件接收相互分離使條件接收系統(tǒng)實現(xiàn)比

- 關(guān)鍵字: FPGA 數(shù)字電視 條件接收系統(tǒng)

基于SRAM的FPGA連線資源的一種可測性設(shè)計

- 本文提出在FPGA芯片內(nèi)插入多條移位寄存器鏈的方法,可使測試開關(guān)盒連線資源的時問比傳統(tǒng)的測試方法和已有的一種方法時間上減少了99%以上,大大降低了測試的時間,降低了測試成本,并且消耗的硬件面積比大約在5%左右,在可接受的范圍內(nèi)。

- 關(guān)鍵字: SRAM FPGA 資源 可測性設(shè)計

NI推出新型原型設(shè)計硬件開發(fā)套件

- 美國國家儀器有限公司(National Instruments,簡稱NI)近日宣布推出新款原型設(shè)計硬件開發(fā)套件,方便工程師和科學家們更快地開展工業(yè)和嵌入式項目的原型開發(fā),縮短產(chǎn)品的上市時間并且減少開發(fā)成本。最新5款NI CompactRIO可重新配置機箱配備Xilinx Virtex-5現(xiàn)場可編程門陣列(FPGA),它是目前NI硬件中容量最大、運行最快的FPGA。此外,新款NI cRIO-9022控制器配備了飛思卡爾(Freescale) 533 MHz工業(yè)實時處理器,為對時間要求極高的控制應用提供更

- 關(guān)鍵字: NI Virtex-5 硬件開發(fā)套件 CompactRIO FPGA

fpga)介紹

您好,目前還沒有人創(chuàng)建詞條fpga)!

歡迎您創(chuàng)建該詞條,闡述對fpga)的理解,并與今后在此搜索fpga)的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga)的理解,并與今后在此搜索fpga)的朋友們分享。 創(chuàng)建詞條

相關(guān)主題

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司