fpga soc 文章 最新資訊

Altera在天津大學(xué)成立國內(nèi)第60所EDA/SOPC聯(lián)合實(shí)驗(yàn)室

- 2009年3月31號,北京——Altera公司(NASDAQ: ALTR)今天宣布,Altera公司于2009年3月10日在天津大學(xué)成立EDA/SOPC聯(lián)合實(shí)驗(yàn)室。這是Altera自2004年3月在中國電子科技大學(xué)成立首個EDA/SOPC聯(lián)合實(shí)驗(yàn)室以來的國內(nèi)第60所聯(lián)合實(shí)驗(yàn)室和培訓(xùn)中心。該實(shí)驗(yàn)室將為數(shù)字邏輯電路、硬件描述語言、微機(jī)原理、電視原理、現(xiàn)代數(shù)字系統(tǒng)設(shè)計(jì)等本科或研究生課程的實(shí)驗(yàn)教學(xué)以及電子類課程設(shè)計(jì)提供支持,Altera®公司的FPGA開發(fā)環(huán)境將成為貫穿天津大學(xué)

- 關(guān)鍵字: Altera FPGA SOPC

MIPS科技贏得重要多媒體手機(jī)設(shè)計(jì)訂單

- 為數(shù)字消費(fèi)、家庭網(wǎng)絡(luò)、無線通信和商業(yè)應(yīng)用提供業(yè)界標(biāo)準(zhǔn)架構(gòu)、處理器和模擬IP的領(lǐng)導(dǎo)廠商 MIPS 科技(MIPS Technologies, Inc)宣布,為新興移動數(shù)字電視(MDTV)和便攜式多媒體市場開發(fā)完整系統(tǒng)級芯片(SoC)解決方案的無晶圓半導(dǎo)體廠商Mavrix科技公司已獲得MIPS32® 4KEc®可合成處理器內(nèi)核授權(quán),用于其下一代媒體處理器設(shè)計(jì)。 Mavrix科技公司首席執(zhí)行官Zhenyu Zhou博士表示:“要在競爭激烈的多媒體手機(jī)市場取得成功,我們的客戶

- 關(guān)鍵字: MIPS SoC MDTV

基于FPGA的高速數(shù)據(jù)采集存儲系統(tǒng)的設(shè)計(jì)

- 0 引言

信息技術(shù)的發(fā)展,特別是各種數(shù)字處理器件處理速度的提高,實(shí)時處理大量的數(shù)據(jù)已經(jīng)成為現(xiàn)實(shí)。但是,在一些惡劣環(huán)境和數(shù)據(jù)無法進(jìn)行實(shí)時傳輸?shù)那闆r下,還必須用到存儲測試的方法。存儲測試是指在對被測對象 - 關(guān)鍵字: FPGA 高速數(shù)據(jù) 采集 存儲系統(tǒng)

2009年3月30日,Altera在天津大學(xué)成立國內(nèi)第60所EDA/SOPC聯(lián)合實(shí)驗(yàn)室

- Altera公司今天宣布,Altera公司于2009年3月10日在天津大學(xué)成立EDA/SOPC聯(lián)合實(shí)驗(yàn)室。這是Altera自2004年3月在中國電子科技大學(xué)成立首個EDA/SOPC聯(lián)合實(shí)驗(yàn)室以來的國內(nèi)第60所聯(lián)合實(shí)驗(yàn)室和培訓(xùn)中心。該實(shí)驗(yàn)室將為數(shù)字邏輯電路、硬件描述語言、微機(jī)原理、電視原理、現(xiàn)代數(shù)字系統(tǒng)設(shè)計(jì)等本科或研究生課程的實(shí)驗(yàn)教學(xué)以及電子類課程設(shè)計(jì)提供支持,Altera®公司的FPGA開發(fā)環(huán)境將成為貫穿天津大學(xué)電子工程類專業(yè)本科和研究生教育階段的實(shí)驗(yàn)平臺。 作為全球領(lǐng)先的可編程邏輯器件

- 關(guān)鍵字: Altera FPGA SOPC

基于FPGA的高速圖像采集系統(tǒng)設(shè)計(jì)

- 在高速圖像采集系統(tǒng)中,CPU時鐘資源、I/O端口資源、傳輸單元等都成為系統(tǒng)的瓶頸。本系統(tǒng)采用FPGA+RAM+USB的設(shè)計(jì):FPGA硬件采樣模塊,有效降低采樣時延和CPU時鐘資源;獨(dú)特的RAM時序控制與讀寫控制分離設(shè)計(jì),增加了模塊之間的獨(dú)立性,降低了控制的復(fù)雜度;USB設(shè)計(jì)在實(shí)現(xiàn)高速率數(shù)據(jù)傳輸?shù)耐瑫r又具有低成本、易安裝等優(yōu)點(diǎn)。

- 關(guān)鍵字: FPGA 高速圖像采集 系統(tǒng)設(shè)計(jì)

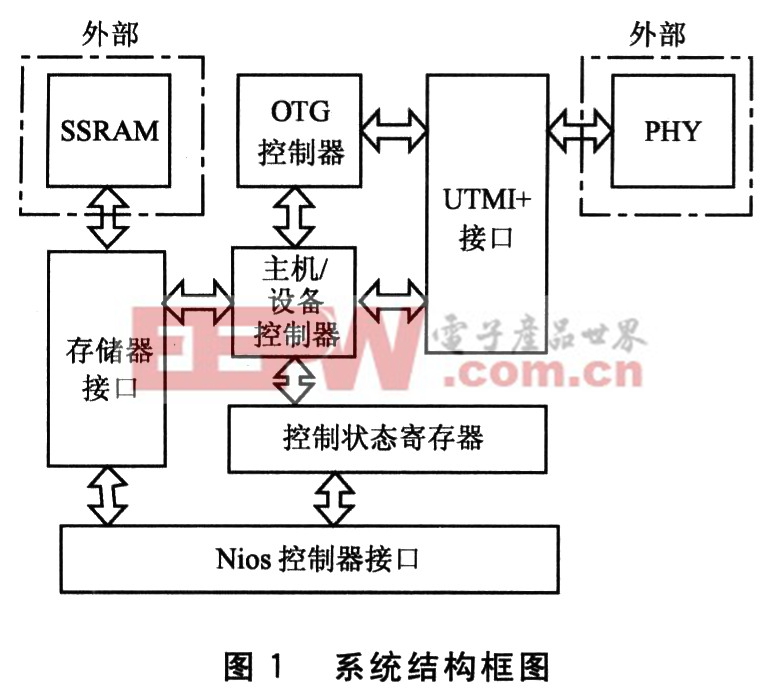

USB OTG的IP Core設(shè)計(jì)與FPGA驗(yàn)證

- 為了實(shí)現(xiàn)USB設(shè)備之間的直接通信,介紹一款USB 0TG IP核的設(shè)計(jì)與FPGA驗(yàn)證。在分析OTG補(bǔ)充規(guī)范的基礎(chǔ)上,重點(diǎn)描述了USB OTG IP核的設(shè)計(jì)原理、模塊劃分以及每個模塊的功能,然后對USBOTG的部分特性進(jìn)行詳細(xì)的闡述,最后給出該IP核在ModelSim中的功能仿真及FPGA驗(yàn)證結(jié)果。結(jié)果表明,該IP核具備主機(jī)功能和設(shè)備功能,可作為一個獨(dú)立的IP模塊應(yīng)用到SoC系統(tǒng)中。

- 關(guān)鍵字: FPGA 驗(yàn)證 設(shè)計(jì) Core OTG IP USB

fpga soc介紹

您好,目前還沒有人創(chuàng)建詞條fpga soc!

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司