- 通過對被測信號的實時采樣,利用等效采樣原理,可以將采樣率為1MHz等效為200MHz,提高了被測信號的最高頻率,具有成本低,性能可靠,便易升級的特點。

- 關鍵字:

采樣 FPGA

- 本視頻介紹的這款智能籃球采用了TI的藍牙低能耗、DSP和Qi兼容的無線充電技術,內置的傳感器能夠測量球員的運球力、投射弧度和拍擊速度等數據,并將它們傳輸到智能手機,以此分析球員的優勢和劣勢。

- 關鍵字:

智能籃球 德州儀器 Qi DSP 藍牙 無線充電

- 開發一款通用性強的網絡數據采集控制器,適合PC(windows與Unix、Linux系統)與片上系統之間的通信(片上運行軟核或硬核嵌入式系統) ,提取的資源是本地控制器參數(如PID參數、射頻信號幅度相位信息和誤差因子等)。

- 關鍵字:

MicroBlaze 采集控制器 FPGA

- 傳統智能小車,特別是嵌入式系統,一般都是基于單片機或者ARM的嵌入式系統,基本上都由軟件系統和硬件系統組成的,硬件系統方面,跟傳統的搭建硬件環境一樣,只能做相對裁剪和功能拓展,但是,本項目的課題是通過xilinx的FPGA開發板搭建嵌入式的硬件環境,從最小系統到IP核的添加,都是根據需要進行拓展的,實現一對一的拓展,不浪費資源,而且基于F

- 關鍵字:

智能小車 Spartan-6 FPGA 電源穩壓芯片 全橋驅動

- 本項目設計方案是基于FPGA的嵌入式安全保密模塊ESMF (Embedded Security Module based on FPGA),并通過高密計算返回安全認證碼,通過安全認證碼與密匙校驗,為用戶解決高密數據存儲、身份認證等很多安全問題,這將為軟件版權的保護提供有效的途徑。

- 關鍵字:

嵌入式安全保密模塊 軟件版權保護 FPGA ESMF

- Atmel公司推出的新一代Atmel32位AVR UC3系列MCU具有1.38 DMIPS/MHz的性能以及先進的DSP算法功能,具有高性能和低功耗特性的特點。因此選用Atmel32位AVR UC3系列MCU作為設計主體實現一個無線圖像偵檢系統,配合協議中的功耗控制,在能夠較好的實現功能的情況下達到節能環保的目的。

- 關鍵字:

AVR單片機 無線圖像偵檢 DSP

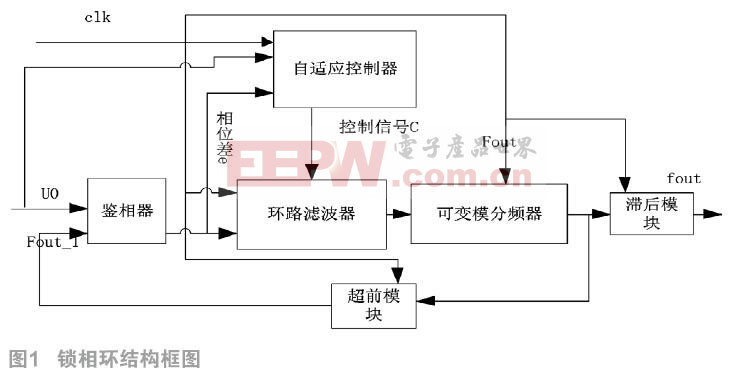

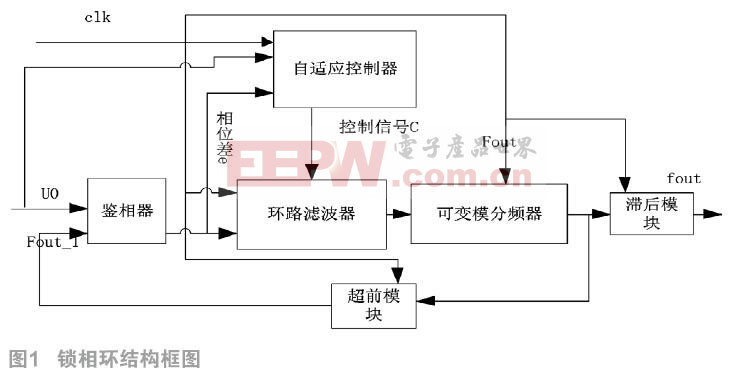

- 針對無線電能傳輸頻率跟蹤設計中傳統鎖相環電路設計復雜、跟蹤速度慢、鎖相頻帶窄和無超前滯后環節,單獨模塊設計修改繁瑣等問題,對自變模全數字鎖相環進行改進, 與傳統的全數字鎖相環相比,該鎖相環采用可變模分頻器,使得中心頻率可變,鎖相范圍增大;通過前饋回路進行鑒頻調頻,提高了鎖相速度;同時,其環路濾波器采用比例積分結構,使得鎖相輸出無靜差且比例積分參數依據相位差自動進行調節;通過參數設置可調節輸出信號的相位。應用modelsim進行仿真,并進行實物驗證證實了該設計具有寬范圍的鎖相能力及快速精確的頻率跟蹤性能。

- 關鍵字:

全數字鎖相環 比例積分控制 FPGA 無線電能傳輸 201706

- 高性能系統設計師在滿足關鍵時序余量的同時要力爭獲得更高性能,而存儲器接口設計則是一項艱巨挑戰。雙倍數據速率SDRAM和4倍數據速率SDRAM都采用源同步接口來把數據和時鐘(或選通脈沖)由發射器傳送到接收器。接收器接口內部利用時鐘來鎖存數據,此舉可消除接口控制問題(例如在存儲器和FPGA間的信號傳遞時間),但也為設計師帶來了必須解決的新挑戰。 關鍵問題之一就是如何滿足各種讀取數據捕捉需求以實現高速接口。隨著數據有效窗越來越小,該問題也益發重要;同時,更具挑戰性的問題是,如何讓接收到的時鐘與數據中心對準

- 關鍵字:

FPGA 存儲器

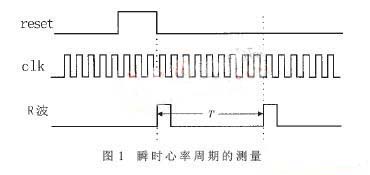

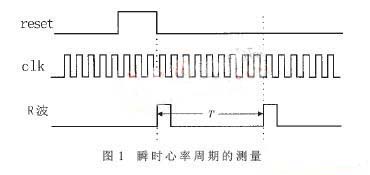

- 心率計是常用的醫學檢查設備,實時準確的心率測量在病人監控、臨床治療及體育競賽等方面都有著廣泛的應用。心率測量包括瞬時心率測量和平均心率測量。瞬時心率不僅能夠反映心率的快慢。同時能反映心率是否勻齊;平均心率雖只能反映心率的快慢,但記錄方便,因此這兩個參數在測量時都是必要的。 測量心率有模擬和數字兩種方法。模擬方法是在給定的時間間隔內計算R波(或脈搏波)的脈沖個數,然后將脈沖計數乘以一個適當的常數測量心率的。這種方法的缺點是測量誤差較大、元件參數調試困難、可靠性差。數字方法是先測量相鄰R波之間的時間,再

- 關鍵字:

FPGA 分頻

- 電子工程師指從事各類電子設備和信息系統研究、教學、產品設計、科技開發、生產和管理等工作的高級工程技術人才。一般分為硬件工程師和軟件工程師。

硬件工程師:主要負責電路分析、設計;并以電腦軟件為工具進行PCB設計,待工廠PCB制作完畢并且焊接好電子元件之后進行測試、調試;

軟件工程師:主要負責單片機、DSP、ARM、FPGA等嵌入式程序的編寫及調試。FPGA程序有時屬硬件工程師工作范疇。

是人就會犯錯,何況是工程師呢?雖然斗轉星移,工程師們卻經常犯同樣的錯誤!下面,就

- 關鍵字:

單片機 DSP

- FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入

- 關鍵字:

FPGA 原理圖

- 雖然英特爾(Intel)、NVIDIA等芯片大廠近期在人工智能(AI)、神經網絡(NN)、深度學習(Deep Learning)等領域動作頻頻,但半導體領域的其他業者也沒閑著,而且其產品發展策略頗有以鄉村包圍城市的味道。 益華計算機(Cadence)旗下的CPU/DSP處理器核心授權公司Tensilica,近期便發表針對神經網絡算法設計的C5 DSP核心授權方案。 在16奈米制程條件下,該核心所占用的芯片面積約僅1平方公厘,卻可提供達到1TMAC的運算效能,而且功耗遠比CPU、GPU等處理器更低,適合

- 關鍵字:

DSP AI

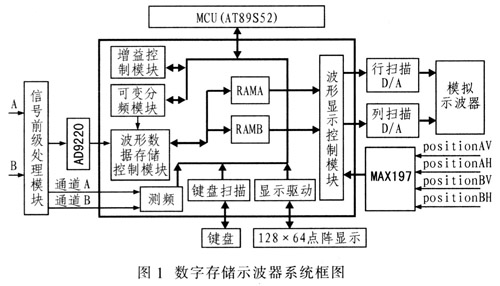

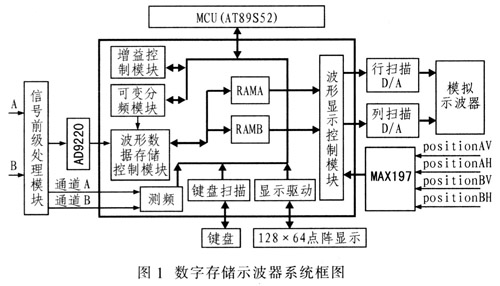

- 與傳統模擬示波器相比.數字存儲示波器不僅具有可存儲波形、體積小、功耗低,使用方便等優點,而且還具有強大的信號實時處理分析功能。在電子測量領域,數字存儲示波器正在逐漸取代模擬示波器。但目前我國使用高性能數字存儲示波器主要依靠國外產品,而且價格昂貴。因此研究數字存儲示波器具有重要價值。借于此,提出了一種簡易數字存儲示波器的設計方案,經測試,性能優良。 2 數字存儲示波器基本工作原理 數字存儲示波器與模擬示波器不同在于信號進入示波器后立刻通過高速A/D轉換器將模擬信號前端快速采樣,存儲其數字化

- 關鍵字:

單片機 FPGA

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473