EEPW首頁(yè) >>

主題列表 >>

非二進(jìn)制

非二進(jìn)制 文章 最新資訊

基于40 nm CMOS工藝的高速SAR ADC的設(shè)計(jì)

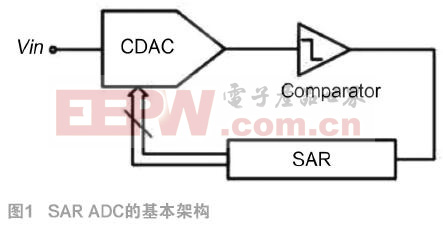

- 基于40 nm CMOS工藝,設(shè)計(jì)了一種高速逐次逼近型模數(shù)轉(zhuǎn)換器。本設(shè)計(jì)采用了非二進(jìn)制冗余DAC技術(shù)來緩解ADC對(duì)建立時(shí)間和建立精度的要求,來提高ADC量化的準(zhǔn)確性;采用帶有預(yù)放大級(jí)的高速比較器來提高比較器的精度,同時(shí)減小后級(jí)Latch的回踢噪聲,采用了兩級(jí)Latch來進(jìn)一步提高比較器的速度;采用基于鎖存器的鎖存單元來提高SAR邏輯控制電路的速度,并且采用了異步時(shí)序控制,不需要外部時(shí)鐘,有利于提高SAR ADC的速度,并降低了設(shè)計(jì)的復(fù)雜度。設(shè)計(jì)的SAR ADC在160 MHz的采樣頻率下,在不同輸入信號(hào)頻

- 關(guān)鍵字: 高速通信 模數(shù)轉(zhuǎn)換器 逐次逼近 非二進(jìn)制 201803

| 共1條 1/1 1 |

非二進(jìn)制介紹

您好,目前還沒有人創(chuàng)建詞條非二進(jìn)制!

歡迎您創(chuàng)建該詞條,闡述對(duì)非二進(jìn)制的理解,并與今后在此搜索非二進(jìn)制的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)非二進(jìn)制的理解,并與今后在此搜索非二進(jìn)制的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司