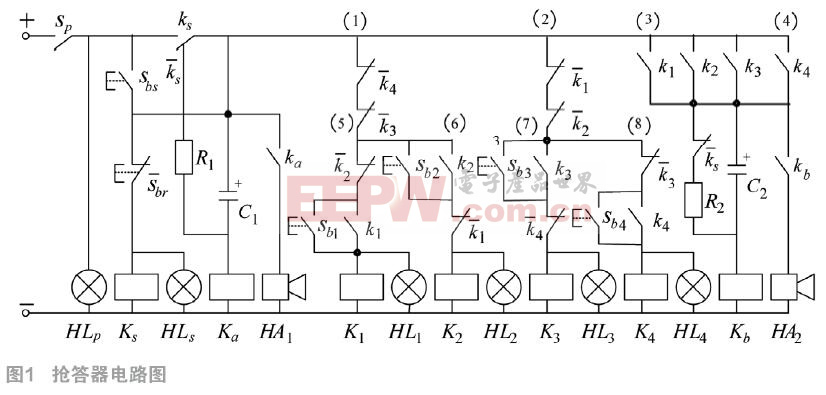

- 本文以四人繼電器型搶答器為例,介紹其邏輯設計方法。該型搶答器的特點是:強抗干擾、工作可靠、結構簡單、維護方便和成本低廉。經使用證明,效果良好。

- 關鍵字:

繼電器 搶答器 邏輯設計 201704

- 入門

結合一兩個小項目把上面所說的事情都做好后,差不多就可以進入入門的階段了(要求稍微嚴格了一點點,呵呵)。

入門階段要學的有:設計時序;理解約束的原理及如何加約束。

先談談設計時序。

設計時序是進行邏輯設計的基本要求:時序是設計出來的,不是仿出來的,更不是湊出來的。

很多人在做邏輯設計時喜歡一上來就狂寫代碼,寫到一半后發現信號間的時序出問題了,只好推倒重來;好不容易反復了幾次之后,通過仿真軟件看了下,差不多要對了,于是再湊一下時序,竟然對了!但這個做法除了設計周期長外,

- 關鍵字:

邏輯設計 時序 約束

- 入門前

剛才開始接觸邏輯設計很多人會覺得很簡單:因為verilog的語法不多,半天就可以把書看完了。但是很快許多人就發現這個想法是錯誤的,他們經常埋怨綜合器怎么和自己的想法差別這么大:它竟然連用for循環寫的一個計數器都不認識!

相信上一段的經歷大部分人都曾有,原因是做邏輯設計的思維和做軟件的很不相同,我們需要從電路的角度去考慮問題。

在這個過程中首先要明白的是軟件設計和邏輯設計的不同,并理解什么是硬件意識。

軟件代碼的執行是一個順序的過程,編繹以后的機器碼放在存儲器里,等著C

- 關鍵字:

邏輯設計 verilog D觸發器

- 我接觸邏輯設計有三年多的時間了,說是三年,其實真正有大的提高就是在公司實習的那一年期間。在即將去公司報到之前,把一些東西寫下來,希望讓大家少走些彎路。

學習邏輯設計首先要有項目掛靠,如果你覺得未來一段時間你都不可能有的話,接下來的內容你就沒有必要再看了,花的時間再多也只能學到皮毛--很多細節的問題光寫代碼是發現不到的。而且要真正入門,最好要多做幾個項目(這三年大大小小的項目我做有七八個),總線型的和數字信號處理型的最好都要接觸一些,因為這兩個方向的邏輯設計差異比較大:前者主要是控制型的,會涉及到

- 關鍵字:

邏輯設計 IC RTL

- 編者按:本文從技術和就業經驗等角度,為即將進入嵌入式開發的工程師們詳細講述嵌入式的概念、嵌入式開發之間的異同以及應該如何做出選擇。是一些經驗之談,希望對大家有所幫助。

一.工程師眼中的“嵌入式系統”

在工程師看來:著重理解“嵌入”的概念,主要從三個方面來理解:

1.從硬件上,將基于CPU 的外圍器件,整合到CPU 芯片內部,比如早期基于X86體系結構下的計算機,CPU 只是有運算器和累加器的功能,一切芯片要靠外部橋路來擴展實現,象串口之

- 關鍵字:

嵌入式系統 邏輯設計 C 語言

- 為了提高溫度保護系統的可靠性,在溫度保護的邏輯設計中可采用容錯設計,即盡可能考慮測溫環節在運行中容易出現的故障,并通過預先設置的邏輯措施來識別錯誤的溫度信號,以防保護系統誤動。

- 關鍵字:

溫度保護 容錯 邏輯設計 系統

- 越來越多企業開始使用變速驅動發動機來減少能源的消耗。這需要通過從微分(PID)控制器轉向基于模糊邏輯算法的系統來簡化設計,縮短開發時間,并消除復雜的數學公式。 但是,這對發動機提出了新的挑戰。當使用傳統

- 關鍵字:

DSP 模糊 邏輯設計 發動機控制器

- 在功能上,單片機與大規模CPLD有很強的互補性。單片機具有性能價格比高、功能靈活、易于人機對話、良好的數據處理能力濰點;CPLD/FPGA則具有高速、高可靠以及開發便捷、規范等優點。以此兩類器件相結合的電路結構在許多高性能儀器儀表和電子產品中仍將被廣泛應用。本文就單片機與CPLD/FPGA的接口方式作一簡單介紹,希望對從事單片機和CPLD/FPGA研發的朋友能有所啟發。 單片機與CPLD/FPGA的接口方式一般有兩種,即總線方式與獨立方式,分別說明

- 關鍵字:

CPLD/FPGA MCS-51 單片機 邏輯設計 嵌入式系統

- CADENCE宣布四家亞太芯片設計公司——Altek 公司、互芯集成電路有限公司(CoolSand Technologies)、韓國電子通信研究院(ETRI)以及 Moai電子公司已經選擇具有全局綜合技術的 Cadence® Encounter® RTL Compiler解決方案,以改良芯片設計,加快上市時間。Encounter RTL Compiler綜合與Encounter Confo

- 關鍵字:

CADENCE 單片機 競爭優勢 邏輯設計 嵌入式系統 通訊 網絡 無線 亞太芯片設計商

- 最新的8.2i升級了ISE,PlanAhead和Chipscope Pro設計軟件 加速設計收斂并為Virtex-5 LXT FPGA提供增強的生產力 賽靈思公司(Xilinx, Inc. (NASDAQ: XLNX))宣布面向最新Virtex™-5 LXT FPGA平臺推出完整的邏輯設計解決方案,包含升級版集成軟件環境(ISE™)設計工具。Virtex™-5&nbs

- 關鍵字:

LXT平 VIRTEX-5 單片機 解決方案 邏輯設計 嵌入式系統 賽靈思

- 最新的8.2i升級了ISE,PlanAhead和Chipscope Pro設計軟件加速設計收斂并為Virtex-5 LXT FPGA提供增強的生產力。 賽靈思公司今天宣布面向最新Virtex™-5 LXT FPGA平臺推出完整的邏輯設計解決方案,包含升級版集成軟件環境(ISE™)設計工具。Virtex™-5 LXT FPGA平臺是業內第一款提供硬代碼PCI Express®

- 關鍵字:

FPGA 邏輯設計 賽靈思

邏輯設計介紹

您好,目前還沒有人創建詞條邏輯設計!

歡迎您創建該詞條,闡述對邏輯設計的理解,并與今后在此搜索邏輯設計的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473