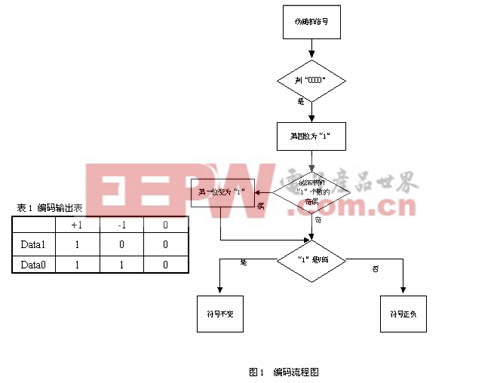

- 基于FPGA的HDB3編解碼器設計,本方案設計模塊可以作為IP(Intellectual Property)核,與嵌入式處理器及其他功能模塊或IP芯核相結合在一片FPGA上構成片上可編程系統SOPC,使得所設計的系統在其規模、可靠性、體積、功耗、性能等方面實現最優化。

- 關鍵字:

設計 解碼器 HDB3 FPGA 基于 編解碼器

- 由于On2的VP7 專有壓縮技術具有種種優勢,因此獲得了市場的廣泛采納。黃金幀、出色的實時質量和解碼器的簡易性,都讓On2 VP7成為目前網絡視頻及未來可能應用的理想選擇。

- 關鍵字:

實時 網絡視頻 高質量 實現 解碼器 黃金 編解碼器

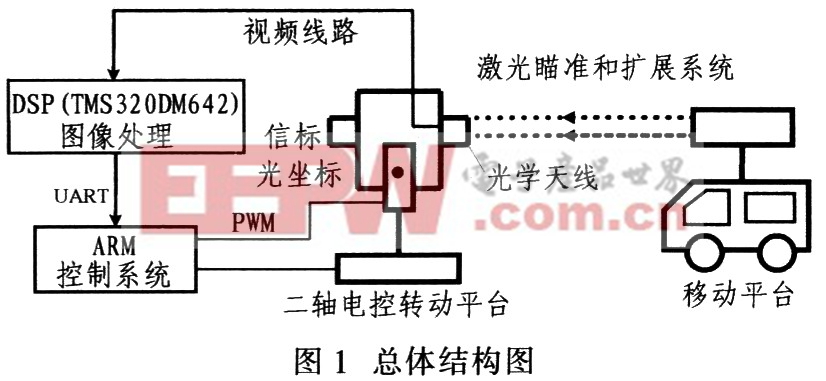

- TMS320DM642在移動平臺ATP技術中的應用,介紹了一種DSP數字處理器TMS320DM642在移動平臺ATP技術中的應用。DSP處理CCD采集的圖像信號,并將相應信息實時反饋給電機控制部分,立即作出相應調整從而控制(2CD運動,使光斑落在視場中心。移動平臺ATP(信標光捕獲跟蹤瞄準)技術是實現空間激光通信的關鍵技術,在衛星和航空航天等大容量通信方面具有巨大應用前景。

- 關鍵字:

技術 應用 ATP 平臺 移動 TMS320DM642 編解碼器

- 確保 QoE:我們需要什么樣的體驗質量?哪些薄弱環節需要加強?如何提高體驗質量?

高級體驗質量將決定電信級互聯網視頻能否得到廣泛推廣。互聯網視頻的體驗質量包羅萬象,比如最后一英里的 IP 數據包交付保證解決

- 關鍵字:

技術 質量監控 體驗 嵌入式 LSI 編解碼器

- 2006年9月,國家廣電總局頒布了我國地面數字電視國家標準,該標準是清華DMB-T方案和上海交大ADTB-T方案的融合體,前者采用單載波調制,后者采用多載波調制。本文介紹了單載波調制和多載波調制的工作原理,以及ADTB-T

- 關鍵字:

對比 分析 技術 標準 數字電視 我國 編解碼器

- 利用多內核處理器的并行編程功能實現視頻代碼轉換,視頻代碼轉換是指從一種壓縮視頻格式轉換為另一種壓縮視頻格式,通常先要把某種格式解碼為原始視頻幀,然后用新的格式重新編碼。在許多應用中高效的代碼轉換至關重要。例如,為了支持視頻點播數據流,視頻數據要以某種主流格式存儲起來以節省空間,但必須支持眾多不同的觀看設備和解碼器。為了做到這一點,需要在數據發送前以實時或者快于實時的速度進行代碼轉換。在視頻節目制作階段進行視頻編輯時,也必須對視頻數據進行解碼、修改和重新編碼。在普通家庭,為了能在家用視頻服務器上使用視頻,視

- 關鍵字:

實現 視頻 代碼 轉換 功能 編程 內核 處理器 并行 利用 編解碼器

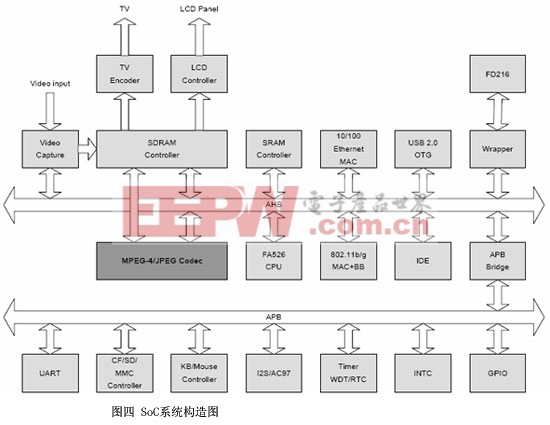

- 隨著硅工藝在幾何尺寸上的不斷縮小,芯片的設計者事實上能將所有系統功能整合在單一芯片上。許多芯片制造商和設計者在面對客戶對于多功能、低功耗、低成本及小型化的需求時,認為SoC的高集成度是解決問題的萬能藥方。不幸的是,設計的生產力跟不上摩爾定律的速度。

- 關鍵字:

MPEG-4/JPEG 解碼 IP 驗證 設計 SoC 平臺 利用 編解碼器

- 基于ARM926EJ-S的MPEG-4軟解碼器的優化與實現,MPEG-4視頻壓縮標準自問世以來受到人們的廣泛關注。近幾年,嵌入式應用中對MPEG-4播放器的實現已經成為眾多廠家的研究熱點。專用的MPEG-4播放芯片已經非常普遍,但是減少功耗和降低成本一直是商家追求的目標,因此,隨著嵌入式的主流微處理器ARM的處理能力越來越強,用他來實現MPEG-4系統的軟解碼成為了眾多嵌入式設計公司研究的重點內容。由于MPEG-4系統龐大且需要大量的數據處理,因此在ARM中實現MPEG-4軟解碼需要對其原算法進行充分的優

- 關鍵字:

優化 實現 解碼器 MPEG-4 ARM926EJ-S 基于 編解碼器

- 介紹了一種多制式語音編解碼器,在單片TMS320VC5409上完成4路話音的全雙工通信,并實現G.729a、CVSD、ADPCM算法之間的編碼轉換,給出了算法的軟硬件實現、算法的運算量及所占用的硬件資源。

- 關鍵字:

DSP 實現 及其 編碼 語音 制式 編解碼器

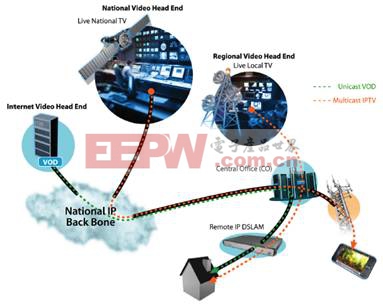

- 網絡電視也稱為IPTV,是三網合一應用中向用戶提供的語音(VoIP)和數據服務之外的第三種服務。現有IPTV用戶中,約80%通過xDSL接入,因此ADSL2+是現階段的首選IPTV操作平臺。盡管VDSL2帶寬更高,但ADSL2+卻擁有覆蓋范圍更廣、成本更低這兩項明顯的優勢。可以預計,在未來數年里,這兩項xDSL技術將繼續被用于IPTV,并且相得益彰。由于xDSL采用常規的銅導線傳輸,而銅導線這種傳輸介質本身易受干擾,因此IPTV有時也會受到影響。現在,已有創新性技術能夠實現無干擾的IPTV接收。

- 關鍵字:

電視 閃爍 接收 IPTV 通過 編解碼器

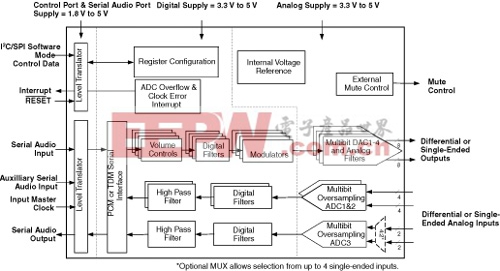

- Cirrus Logic最近推出多款環繞聲編解碼器。該系列產品將幫助音視頻接收器及車載音響系統制造商將多通道環繞聲性能整合到自己的入門級和中檔產品中。

- 關鍵字:

系統 設計 門檻 音頻 降低 環繞 解碼器 集成 編解碼器

- 根據低碼率實時應用領域的特點,設計了一種H.264視頻編碼系統。采用FPGA的NiosII CPU架構,自定義硬件模塊實現H.264.實時壓縮編碼。實驗驗證表明,H.264編碼器對CIF大小的圖像實現了實時編碼,能滿足對低碼率實時應用的編碼要求。

- 關鍵字:

編解碼器 H.264 NiosII CPU

編解碼器介紹

編解碼器(codec)指的是一個能夠對一個信號或者一個數據流進行變換的設備或者程序。這里指的變換既包括將信號或者數據流進行編碼(通常是為了傳輸、存儲或者加密)或者提取得到一個編碼流的操作,也包括為了觀察或者處理從這個編碼流中恢復適合觀察或操作的形式的操作。編解碼器經常用在視頻會議和流媒體等應用中。

經過編碼的音頻或者視頻原始碼流經常被叫做“Essence”(有譯作“本體”,“精”),以區別于 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473