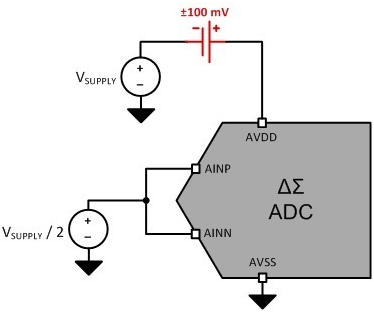

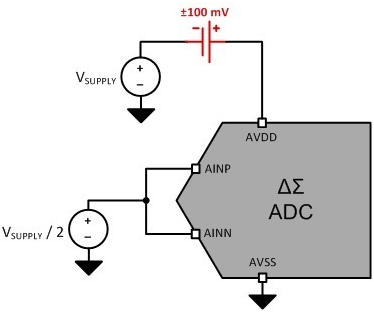

- 筆者曾聽人把電源形容成“電路的鞋帶。”像電路一樣,人們常為鞋子的設計和款式做大量艱苦的工作,卻直到最后才會想起鞋帶。雖然電源往往是后添加的東西,但它們的設計可能正如信號鏈本身一樣重要。 在本系列的第一部分,筆者將介紹電源抑制(PSR)的概念,并說明電源如何能影響Δ-Σ型模數轉換器(ADC)的性能。 筆者的直流(DC)電源“固如磐石”,對嗎? 您的電源也許并不如您想象的那樣堅固耐用,信不信由您。從DC的角度來看,組件容差和溫度漂移都可能導致您的電源輸出因電路板不同和溫度變化而發生變化。輕微的變化似

- 關鍵字:

模數轉換器 PSR

- 本文主要介紹了ADC和DAC常用的56個技術術語,如“采集時間”、“混疊”、“孔徑延遲”等,幫助初學者更好的理解專業術語。 采集時間 采集時間是從釋放保持狀態(由采樣-保持輸入電路執行)到采樣電容電壓穩定至新輸入值的1 LSB范圍之內所需要的時間。采集時間(Tacq)的公式如下:

混疊 根據采樣定理,超過奈奎斯特頻率的輸入信號頻率為“混疊”頻率。也就是說,這些頻率被“折疊”或復制到奈奎斯特頻率附近的其它頻譜位置。為防止混疊,必須對所有有害信

- 關鍵字:

ADC DAC

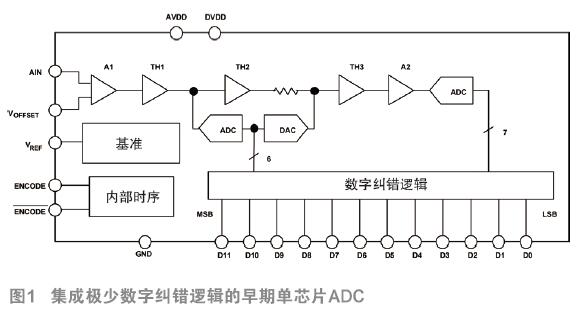

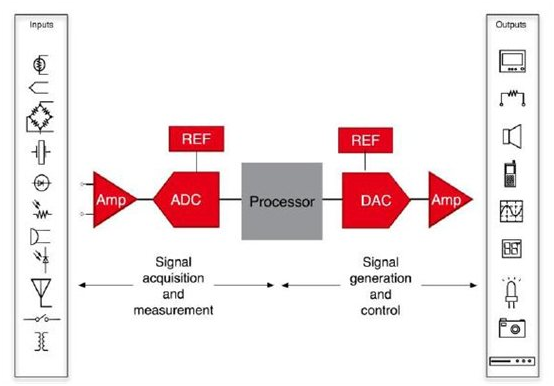

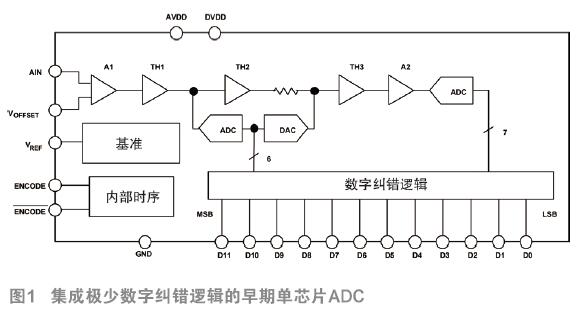

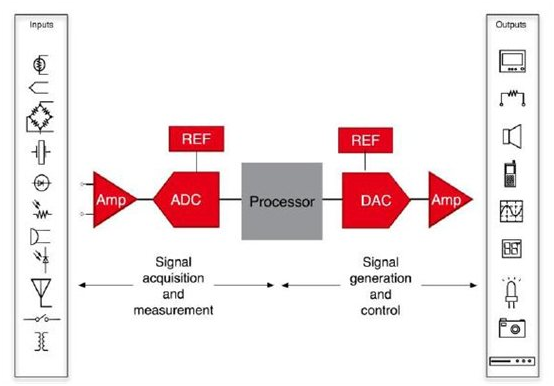

- 數據轉換器現已蛻變為高度集成的單芯片IC。從第一款商用數據轉換器誕生以來,對更快數據速率的無止境需求驅動著數據轉換器不斷向前發展。目前ADC的最新產品是采樣速率達到GHz的RF采樣ADC。更高帶寬的需求伴隨著更高容量的需求,這就給FPGA I/O帶來了更大的壓力,而RF采樣ADC可以利用內部DDC予以化解。

- 關鍵字:

ADC RF采樣 GHz 201603

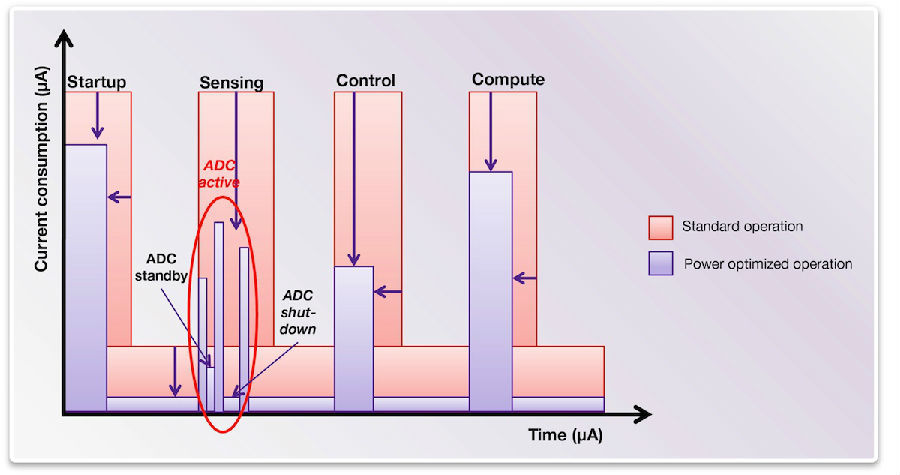

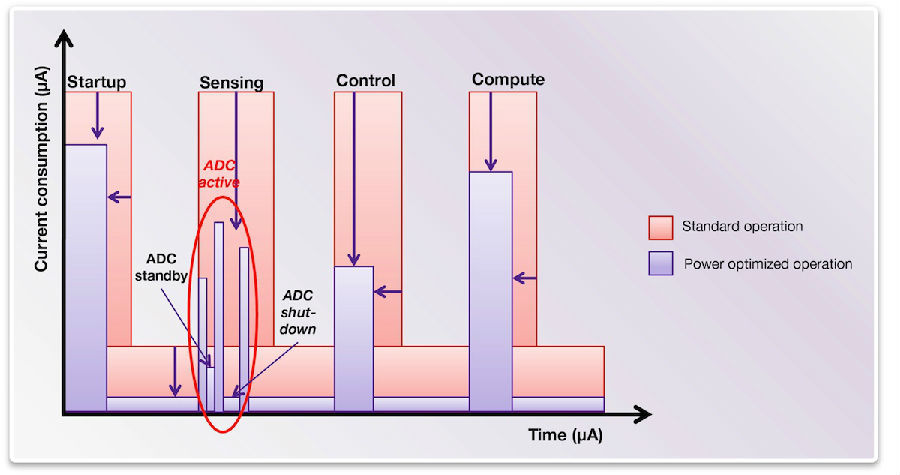

- 諸如物聯網(IoT)這樣的功耗敏感型應用要求在系統級芯片(SoC)內部有一套全面的低功耗策略。單純依賴傳統關閉電源模式和低電源電壓的技術可能不足以實現功耗目標。模擬模塊通常被認為是過于敏感,并且與激進的電源管理技術不兼容。 然而,對于模擬模塊特性的全面了解可以使低功耗SoC設計成為可能。在本文中,我們對通用的物聯網SoC設計中與外部傳感器連接的模數轉換器(ADC)知識產權(IP)進行了近距離的觀察,并描述了其相關特性,以及在系統層面上如何利用這些特性來實現低功耗。 傳統低功耗技術的挑戰 那些有可

- 關鍵字:

模數轉換器 物聯網

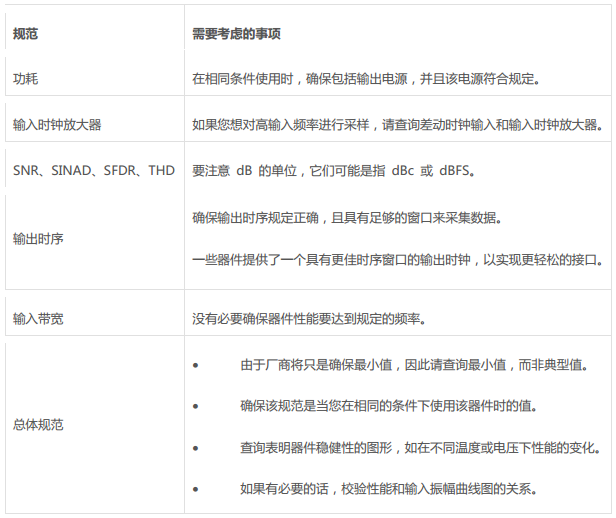

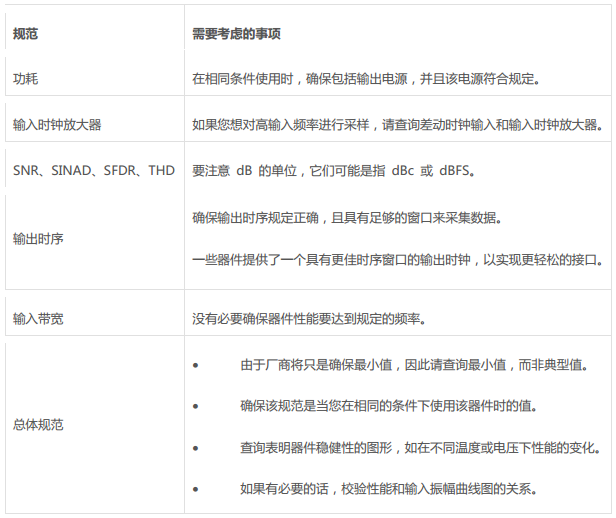

- 和一個產品的任何其他方面一樣,產品說明書也可以得到不斷的改進,廠商正努力地詳細闡明產品說明書1。然而,市場上已經遺留了許多產品/產品說明書版本,對新版本或者更早的版本來說,不同標準的采用也取決于不同的因素。即使有一些特定的標準已經公開發表(如參考書目 2 所提到的),標準的統一仍然是遙遙無期。 本文的目的就在于突出不同廠商或同一廠商在為不同的高速模數轉換器 (ADC) 撰寫產品說明書時所采用的標準之間的差異。表 1 是選擇正確器件時可以使用

- 關鍵字:

TI ADC

- 最近幾年,高速、高精度的模數轉換器變得疾速。在 2006 年,一款業界一流的 12-位轉換器才達到 250 兆采樣/秒 (MSPS)。而今天,這一速度已經翻了一番,達到了 500 MSPS。14-位和 16-位精度的類似發展趨勢也日益明顯。這表明,在比特精度不變的條件下,ADC 速度正以幾乎每年翻一番的速度發展。采樣速率增長的結果是,收斂數字時序來確保您終端系統的數據完整性正變得越來越重要。 要收斂時

- 關鍵字:

ADC

- 在您開始設計以前,首先要看一下您想要數字化的信號類型。例如,如果您知道系統所有通道的最高、最低頻率以及精度要求,那么您可能會需要數個 ADC。 另一種情況下,這些通道可能具有互不相同的時間關系,這就要求一種能夠保護相位信息的同時采樣方法。您可以利用采樣保持電路和一個 ADC 來達到這一目的,而使用獨立的 ADC 可能會更容易一些。 圖 1 顯示了一個 Δ-Σ 轉換器多路復用電路,在該多路復用器的信號端上有一些

- 關鍵字:

轉換器 ADC

- 本文給大家分享了ADC學習知識。

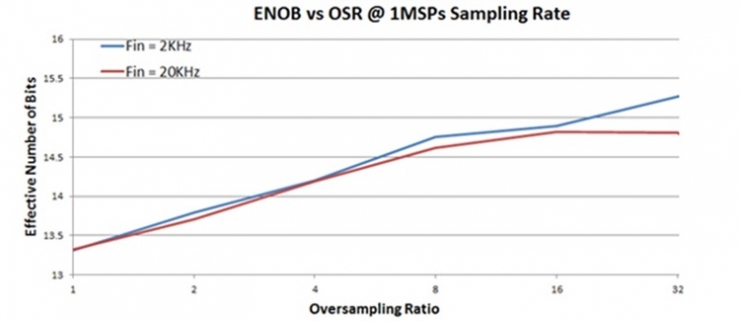

過采樣頻率:增加一位分辨率或每減小6dB 的噪聲,需要以4 倍的采樣頻率fs 進行過采樣.

假設一個系統使用12 位的ADC,每秒輸出一個溫度值(1Hz),為了將測量分辨率增加到16 位,按下式計算過采樣頻率: fos=4^4*1(Hz)=256(Hz)。

1. AD轉換器的分類下面簡要介紹常用的幾種類型的基本原理及特點:積分型、逐次逼近型、并行比較型/串并行型、Σ-Δ調制型、電容陣列逐次比較型及壓頻變換型。 ?

1)

- 關鍵字:

ADC 基準源

- 系統設計人員正面臨越來越多的挑戰,他們需要在不降低系統組件(例如:高速 數據轉換器)性能的情況下讓其設計最大程度地節能。設計人員們可能會轉而采 用許多電池供電的應用(例如:某種手持終端、軟件無線設備或便攜式超聲波掃 描儀),也可能會縮小產品的外形尺寸,從而需要尋求減少發熱的諸多方法。 極大降低系統功耗的一種方法是對高速數據轉換器的電源進行優化。數據轉換器設計和工藝技術的一些最新進展,讓許多新型ADC可以直接由開關電源來驅 動,從而達到最大化功效的目的。 系統

- 關鍵字:

ADC LDO

- 行業分析師們一致認為未來系統的發展趨勢是移動便攜、"綠色"節能,以及在終端設備中集成更多的傳感器。這種發展趨勢,要求模數 (ADC) 轉換器和數模 (DAC) 轉換器具有更多的通道數、更高的速度和性能,同時還要求更低的功耗預算、更小的尺寸以及更低的成本。 各大數據轉換器廠商通過制造更多集成了其他電路組件的數據轉換器對這些需求做出了積極的響應。盡管在許多微處理器內核周圍有大量的外圍設備,一些性能需求正推動許多特殊模擬前端或者其他模擬"

- 關鍵字:

TI ADC

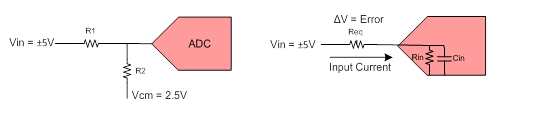

- 本文根據一個實用的電路設計闡述了如何設置高速ADC MAX1196的共模輸入范圍。 輸入共模電壓范圍(Vcm)對于包含了基帶采樣和高速ADC的通信接收機設計非常重要,尤其是采用直流耦合輸入、單電源供電的低壓電路。對于單電源供電電路,饋送到放大器和ADC的輸入信號應該偏置在Vcm范圍以內的直流電平,能夠消除放大器和ADC設計的一大屏障,因為不必在0V保持低失真和高線性度。 直接下變頻結構的無線通信接收機通常采用差分、直流耦合方式與ADC連接。這種電路包含一個零中頻(ZIF)結構,具有一個R

- 關鍵字:

ADC MAX1196

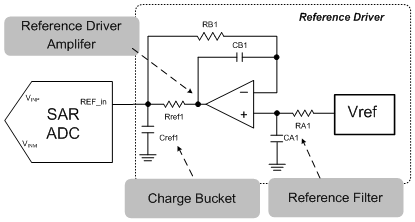

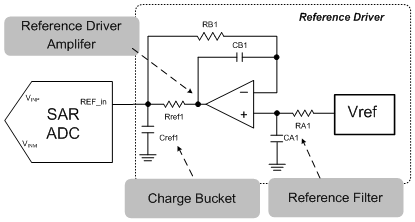

- “聰明的人解決問題,智慧的人避免問題。”— 阿爾伯特·愛因斯坦 愛因斯坦也許也會愛上模擬設計,因為其中總會涉及一些相對論。例如在數據采集系統中,精確度是相對于數據轉換器參考電壓的。 當模數轉換器 (ADC) 不含內部參考時,數據采集系統就需要外部電壓參考電路。讓電路板及系統級設計人員非常苦惱的是, 這通常是精確數據采集系統性能不佳的源頭。ADC的轉換精度基于這些電路為ADC提供的精確電壓。 好消息是有三個重要組件可幫助優化外部參考電路,提高 ADC 性能。它們分別是:電壓參考、參考驅動器放大器和

- 關鍵字:

數據采集 ADC

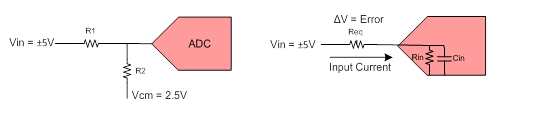

- 工程師們喜歡通過多種方法簡化設計流程。我最喜歡的是一直采用低阻抗電源驅動模數轉換器 (ADC) 輸入。為什么我會對這種方法情有獨鐘?因為它可為精確數據采集模塊帶來諸多優勢。 我們首先來看一種常見應用,其中需要將高電壓信號源進行電平轉換,將其轉換為所需的 ADC 輸入范圍。圖 1 中的簡單分壓器可用來解決該問題,即將 +/-5V 信號電平轉換為 0-5V。該分壓器的等效阻抗 Req等于 R1 與 R2 的并行結合。 那么,這種有限電源阻抗會如何影響數據采集系統? 圖1 高電源阻抗會在數據采集過程

- 關鍵字:

ADC SNR

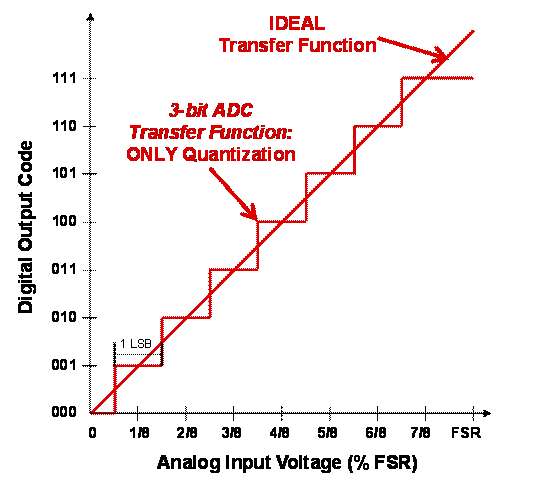

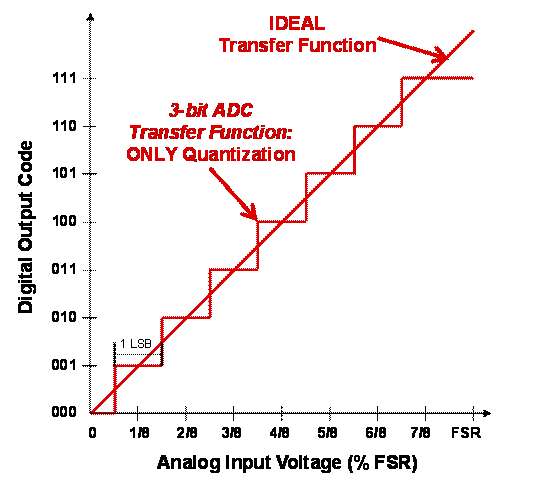

- 上周,我把家里的地毯換成了木制地板。在移除客廳樓梯的地毯后,我注意到原本“一致”的樓梯臺階的進深寬度其實很不均勻。對此,我感到非常驚奇,因為這么多年來我上上下下卻從未注意到臺階是不均勻的。這是因為地毯絕妙地掩蓋了這個問題。 以我書呆子式的思維方式,這件讓我不禁想到了高分辨率 SAR 模數轉換器 (ADC) 的問題。我原本以為我家的樓梯是均勻的,就像具有完美對稱的量化步進的無噪聲 ADC 的理想轉換函數一樣。圖 1 顯示了 3 位 ADC 的實例情況。 圖1.ADC 轉換函數——“均勻一致的樓梯”

- 關鍵字:

ADC SAR

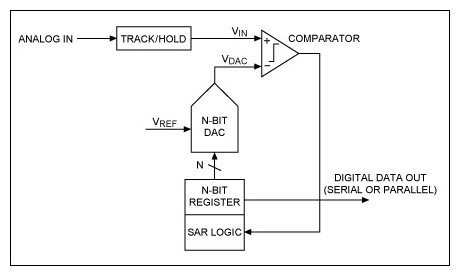

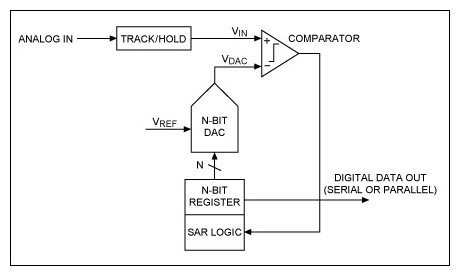

- 本文說明了SAR ADC的工作原理,采用二進制搜索算法,對輸入信號進行轉換。本文還給出了SAR ADC的核心架構,即電容式DAC和高速比較器。最后,對SAR架構與流水線、閃速型以及Σ-Δ ADC進行了對比。 逐次逼近寄存器型(SAR)模擬數字轉換器(ADC)是采樣速率低于5Msps (每秒百萬次采樣)的中等至高分辨率應用的常見結構。SAR ADC的分辨率一般為8位至16位,具有低功耗、小尺寸等特點。這些特點使該類型ADC具有很寬的應用范圍,例如便攜/電池供電儀表、筆輸入量化器、工業控制和數據/信號采

- 關鍵字:

ADC SAR

模數轉換器(adc)介紹

您好,目前還沒有人創建詞條模數轉換器(adc)!

歡迎您創建該詞條,闡述對模數轉換器(adc)的理解,并與今后在此搜索模數轉換器(adc)的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473