如何利用GPS OEM來進行二次開發,產生高精度時鐘發生器是一個研究的熱點問題。在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS時鐘發生器(GPS同步時鐘)對維持系統正常運轉有至關重要的意義。如在DVB-T單頻網(S

關鍵字:

方案 技術 發生器 時鐘 GPS

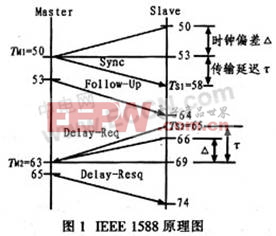

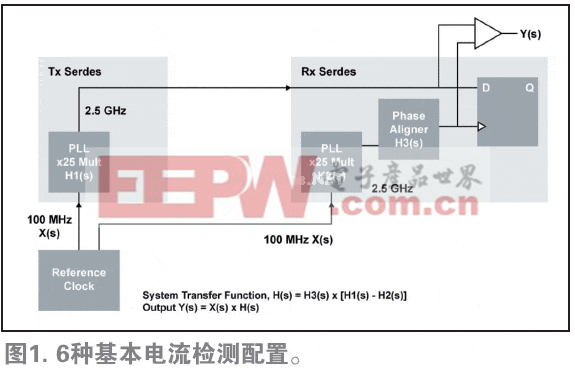

為實現分布式系統高精度同步數據采集及實時控制,提出一種基于IEEE 1588協議的分布式系統時鐘同步方法。通過分析影響同步精度的因素,采用FPGA設計時間戳生成器,并且采用晶振頻率補償時鐘解決時間戳的精確獲取和從時鐘相對主時鐘的頻率糾偏等問題。

關鍵字:

分布式 系統 應用 技術 同步 IEEE 時鐘 基于 收發器

高性能模擬與混合信號IC領導廠商Silicon Laboratories (芯科實驗室有限公司)今日發表在線時鐘樹設計服務,客戶可利用此服務迅速獲得Silicon Labs經驗豐富的應用工程團隊提供的定制化時鐘架構建議,進一步簡化設計、降低BOM材料成本,將開發風險降至最低。此外,Silicon Labs可提供業界最短的元器件交貨期(約兩星期或更短時間),從而大幅加速客戶產品的上市時間。

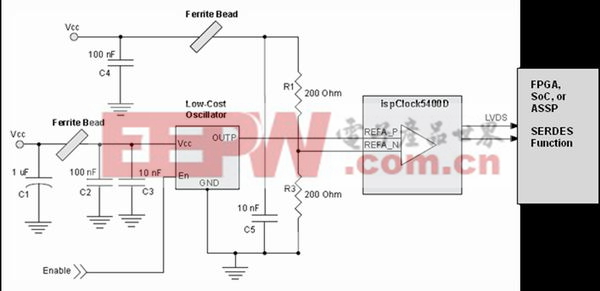

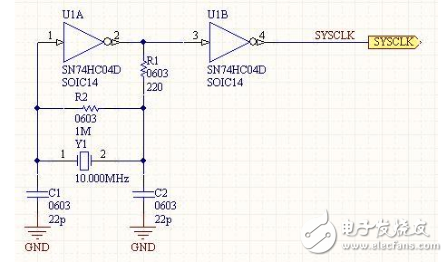

在強調性能的應用中,通常采用振蕩器、時鐘發生器和頻率緩沖器的組合,為高速SerDes元器件、FPGA、處理器

關鍵字:

芯科實驗室 時鐘

針對X光安檢機系統控制信號傳輸中采用傳統串行通信方式所存在的問題,提出一種利用數字鎖相環技術實現串行數據時鐘提取的硬件解決方案。該設計基于FPGA進行開發,并針對安檢機中串行控制數據傳輸的數字鎖相環進行研究,設計了適用于FPGA的串行時鐘提取系統,最終采用Verilog語言實現。該設計經過安檢機系統的硬件平臺實際測試,最終經過Signal TapⅡ讀取實時數據進行驗證,可以論證該方案的時鐘捕捉周期短,捕捉精度也滿足安檢機系統要求,從而實現了安檢機系統數字控制信號的單線路傳輸,有效地提高傳輸的可靠性。

關鍵字:

設計 實現 提取 時鐘 控制 信號 安檢 時鐘提取

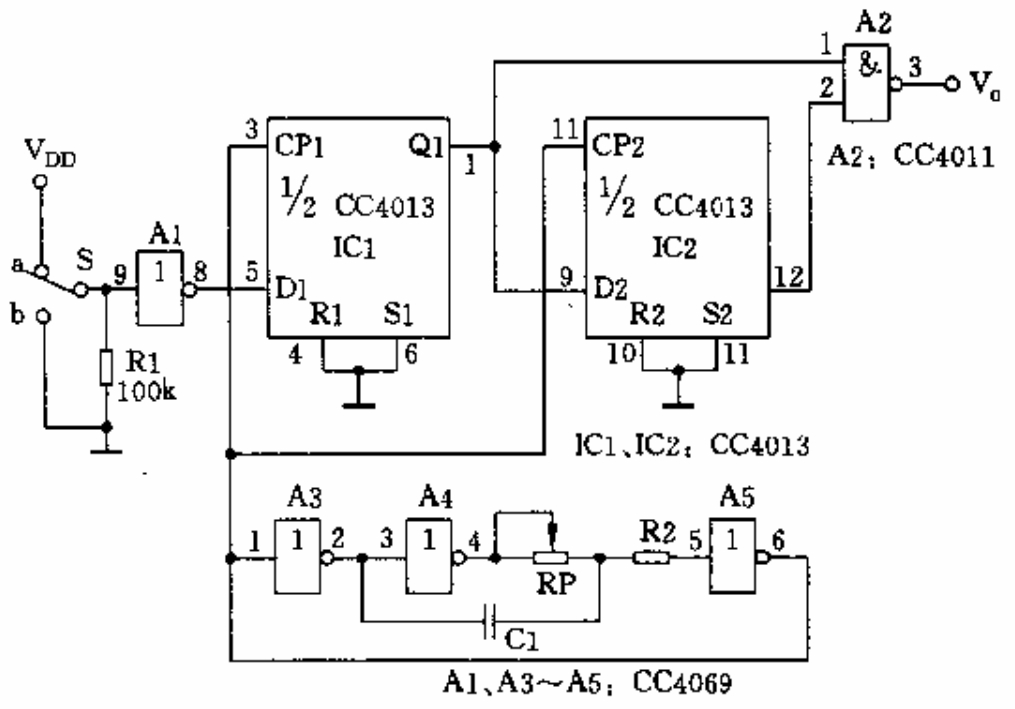

圖3.23所示的電路,是一個16進制的反相器,用于產生30~160NS的延遲。每一級的延遲時間是5~35NS,具體數值由可變電阻的值決定。每一級的延遲時間不應該超過時鐘周期的12%,以保重穩定工作。通過調整延遲級數(2或4)并

關鍵字:

時鐘 簡單電路 相位調整

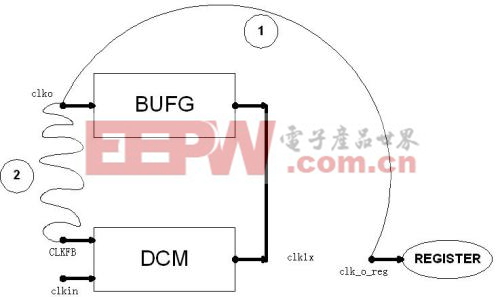

FPGA DCM時鐘管理單元簡介及原理,DCM概述

關鍵字:

簡介 原理 單元 管理 DCM 時鐘 FPGA

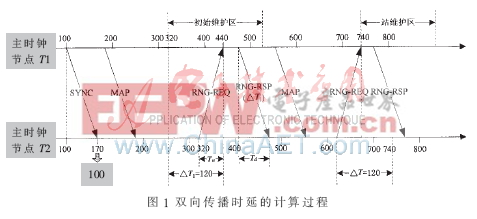

Ad hoc網絡是一種特殊的無線移動通信系統,具有無中心、多跳等特點。結合無線傳感器網絡時鐘同步協議RBS、TPSN和有線網絡DOCSIS協議,提出了一種適合Ad hoc網絡的時鐘同步協議。先在Ad hoc網絡上建立具有層次性的全網絡結構后,以發送廣播時鐘同步信號的方式實現全網絡節點的時鐘相對同步,并通過周期性和突發性的雙向測距實現和維護主從時鐘節點之間精確的時間同步,以滿足實際應用的要求。仿真實驗表明,該時鐘同步協議能滿足不同時鐘同步精度要求下的Ad hoc網絡應用,具有低功耗和高可靠性的特點。 關鍵字:

時鐘 同步 協議 測距 網絡 Ad hoc 基于 通信協議

Analog Devices Inc.,全球領先的高性能信號處理解決方案供應商和數據轉換技術領先者,最近推出兩款時鐘產品 AD9553和 ADCLK944。這些產品用于完整時序信號鏈中時,可提高同步光纖網絡和無線基站的性能,并降低編程和設計復雜度。

時鐘發生器 AD9553適合 GPON、SONET/SDH OC-48(同步光纖網絡/同步數字體系)、測試和測量、數據采集、以太網、光纖通道、T1/E1、廣播視頻及其它無線和有線通信應用的低成本時鐘轉換需求。

ADCLK944旨在改善無線基站中

關鍵字:

ADI 時鐘 數據轉換 AD9553 ADCLK944

給出異步FIFO電路在高速數據采集系統中的應用,由FPGA生成獨立時鐘域的FIFO緩存器,采用FIFO的可編程設置參數啟動數據傳輸,根據讀寫時鐘頻率異同的傳輸要求和FIFO的特性,采用一套控制電路,解決了可變速率數據緩存和固定時鐘傳輸的問題。

關鍵字:

FIFO FPGA 時鐘 201004

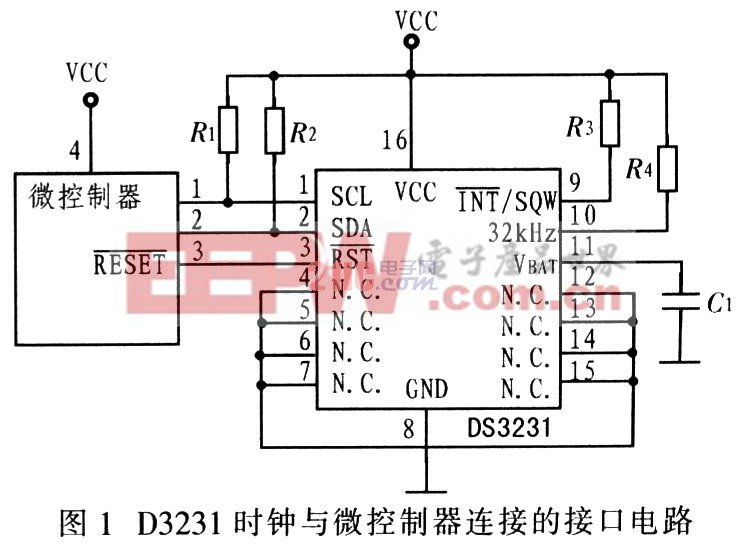

摘要:為避免電路系統在上電或斷電后出現計時不準確的異常狀況,提出采用高精度時鐘芯片DS3231的解決方案。介紹DS3231的特點、工作原理以及引腳功能,設計其與微控制器進行通信時的軟件、硬件接口,并給出相應的原理

關鍵字:

接口 設計 時鐘 高精度 DS3231 基于

高速串行接口設計的高效時鐘解決方案,數字系統的設計師們面臨著許多新的挑戰,例如使用采用了串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架構。基于SERDES的設計增加了帶寬,減少了信號數量,同時帶來了諸如減少布線沖突、降低開關噪

關鍵字:

時鐘 解決方案 高效 設計 串行 接口 高速

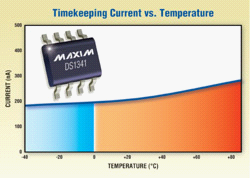

Maxim推出RTC (實時時鐘)產品線的最新成員DS1341。該款RTC集成AGC (自動增益控制)電路,動態調節驅動電流,使器件正常工作時的電流損耗降至最低。此外,器件還支持高ESR晶體,為系統設計人員在晶體選擇上提供了極大的靈活性。DS1341集節電和靈活的晶體選擇特性于一體,非常適合用于醫療、銷售終端機(POS)、汽車及便攜設備。

器件的地址和數據可通過I²C串行接口訪問,其它特性包括:兩個定時鬧鐘、兩路中斷輸出、一路可編程方波輸出以及串行總線超時機制。時鐘/日歷提供秒、分鐘、

關鍵字:

Maxim 時鐘 DS1341 RTC

摘 要:為了保證管道輸送的正常運行,對管道進行破壞預警監測具有極為重要的現實意義,快速、準確地判定事發地點是預警監測的重要內容。設計了管道預警監測及定位的系統方案,分析了其監測定位原理,并指出破壞聲波

關鍵字:

GPS 時鐘 定位

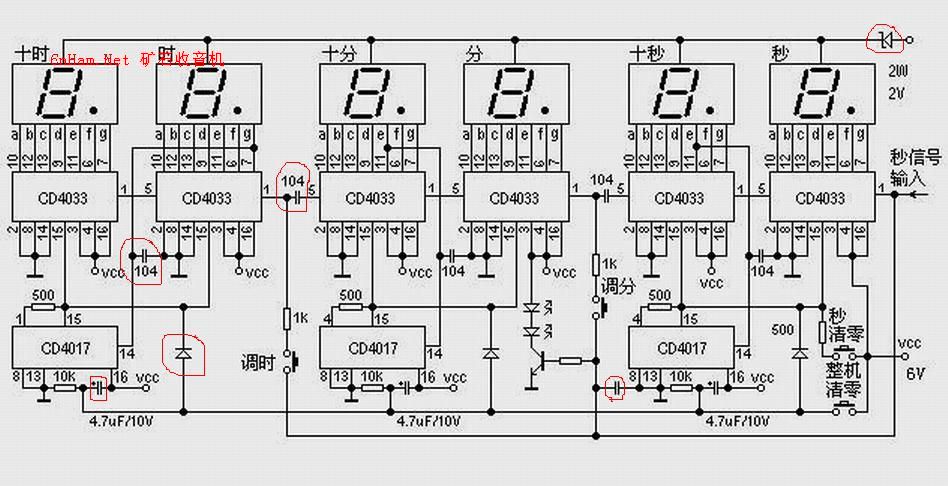

我們以一個實際的時鐘電路來說明定時器的軟件編程方法,時鐘就是我們最為常見的顯示時、分、秒為單位的計時工具,它是典型的應用代表。

關鍵字:

原理 電路 時鐘 組成 AT89C2051

嵌入式系統的PCI Express時鐘分配, PCI Express (PCIe)是嵌入式和其它系統類型的背板間通信的一個非常理想的協議。然而,在嵌入式環境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得并不理想。本文將討論如

關鍵字:

時鐘 分配 Express PCI 系統 嵌入式

時鐘介紹

時鐘的概念多用于數字語音交換機,因為數字交換對于以時隙為單位的交換單位而言,其時間性的重要程度非常高。為保證交換機的正常工作,每套交換系統都必須配置精度極高的時鐘發生器,用于交換系統內部工作。系統內部的時鐘一般稱為內時鐘。

如果兩套交換系統協調工作,那么必須要在兩套系統之家,也就是兩個內時鐘之間進行協調,保證兩個時鐘同步工作,這就是時鐘同步,對于每套系統的內時鐘而言,另一套系統的內時鐘即為外時鐘 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473