- 01 前言在產品開發時,經常會碰到在測試過程中或設備出廠后才發現程序異常,但當重新對設備仿真調試時卻復現不出現場的問題,或者只能通過保存的日志信息艱難分析代碼運行到了何處而導致的異常。 遇到這種場景,也并非無路可循。原則上只要我們通過仿真器調試時,做到代碼不被重新下載覆蓋,MCU 不被復位,就可能保留當前程序運行的狀態,讓 Bug 無處藏身。02 實現方法首先,我們將編譯完成的工程燒錄到 MCU,保證 MCU 中所運行的代碼與要仿真的工程代碼一致,這樣從 MCU 獲取的程序位置才能與調試符號信息

- 關鍵字:

MCU 復位 仿真器

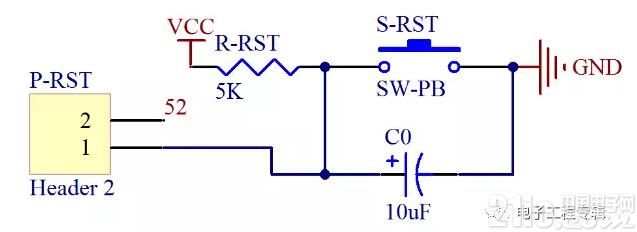

- 電源、時鐘和復位電路圖(Altera FPGA開發板).

- 關鍵字:

復位 電源 時鐘

- FPGA(Field-Programmable?Gate?Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入

- 關鍵字:

FPGA 復位

- 可能的原因:也許,您該檢查一下您的電源走線是不是夠粗,或者,程序是不是一開始運行就點亮LED或者叫BUZZER?因為,PICmicro開始任務的電壓通常是蠻低的。如果因為上述原因而讓電壓驟降,可能會讓Vcc電壓瞬間掉至reset電壓以下,而造成重置。如果您的示波器不夠好,很有可能根本觀察不到此電壓變動之狀況。 WDT TIMEOUT 的標準時間為18mSec, 但是非常重要的一點, WDT TIMEOUT 的最小值為7~9mSec, 而且會受溫度的影響

- 關鍵字:

PIC 復位

- 接口確定以后,FPGA內部如何規劃?首先需要考慮就是時鐘和復位。

時鐘:根據時鐘的分類,可以分為邏輯時鐘,接口時鐘,存儲器時鐘等;

(1)邏輯時鐘取決與邏輯的關鍵路徑,最終值是設計和優化的結果,從經驗而不是實際出發:低端FPGA(cyclone spantan)工作頻率在40-80Mhz之間,而高端器件(stratix virtex)可達100-200Mhz之間,根據各系列的先后性能會有所提升,但不是革命性的。

(2)接口時鐘,異步信號的時序一般也是通過FPGA片內同步邏輯產生,一般

- 關鍵字:

FPGA 架構設計 復位

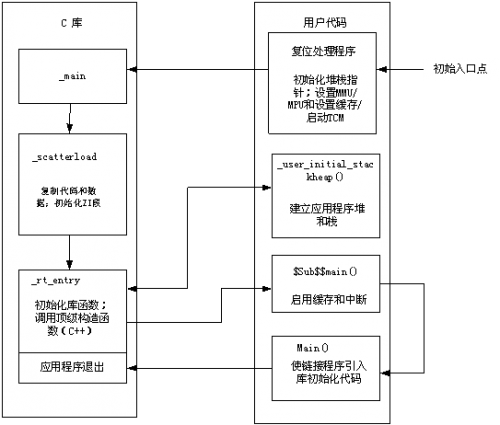

- 13.5 復位和初始化

任何運行在實際硬件上的嵌入式應用程序,都必須在啟動時實現一些基本的系統初始化。本節將對此予以詳細討論。

13.5.1 初始化序列

圖13.14顯示了一個適用于ARM嵌入式系統的初始化序列。

圖13.14 ARM嵌入式系統的初始化序列

系統啟動時立即執行復位處理程序,然后進入$Sub$$main()的代碼執行。

復位處理程序是用匯編語言編寫的代碼塊,它在系統復位時執行,完成系統初始化操作。對于具有局部存儲器的內核,如

- 關鍵字:

嵌入式 復位 初始化

- 本文旨面向初級工程師或是剛剛升遷的而又想掌握一些技術管理者們。

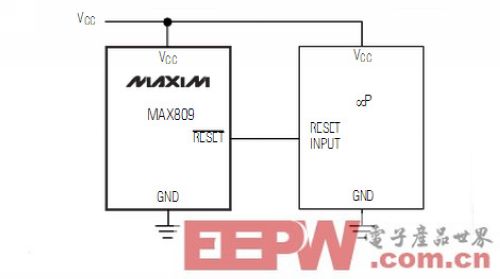

微處理器是一個復雜又單一的東西。它啟動的方式一成不變,嚴格、準確地重復地執行著函數功能。我們可以當微處理器已經穩定進入啟動程序后,發送一個復位操作來讓微處理器執行正確的程序指令。當復位信號結束,微處理器的部分寄存器(根據微處理器型號而不同)將會重新初始化為默認值。微處理器也會從一個固定的地址重新開始執行。因此,設計一個復位方案對于避免系統鎖死、執行程序出錯或者是非易失性flash讀寫錯誤導致的系統崩潰將是非常致關重要的。

其實

- 關鍵字:

微處理器 復位 復位電路

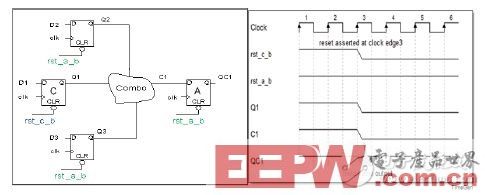

- 隨著數字化設計和SoC的日益復雜,復位架構也變得非常復雜。在實施如此復雜的架構時,設計人員往往會犯一些低級錯誤,這些錯誤可能會導致亞穩態、干擾或其他系統功能故障。本文討論了一些復位設計的基本的結構性問題。在每個問題的最后,都提出了一些解決方案。

復位域交叉問題

1. 問題

在一個連續設計中,如果源寄存器的異步復位不同于目標寄存器的復位,并且在起點寄存器的復位斷言過程中目標寄存器的數據輸入發生異步變化,那么該路徑將被視為異步路徑,盡管源寄存器和目標寄存器都位于同一個時鐘域,在源寄存器的復位斷言過程中可

- 關鍵字:

SoC 復位

- 1、指令冗余

CPU取指令過程是先取操作碼,再取操作數。在程序的關鍵地方人為的插入一些單字節指令,或將有效單字節指令重寫稱為指令冗余,通常是在雙字節指令和三字節指令后插入兩個字節以上的NOP指令。這樣即使跑飛程序飛到雙字節指令和三字節指令操作數上。由于窄操作指令NOP的存在,避免了后面的指令被錯誤地執行,為程序納入正軌做好準備。此外,對系統流向起重要作用的指令,如RET、RETI、LCALI.、LJMP,JC等,可以在這些指令之后插入兩條NOP指令,可將跑飛程序納入正軌,以確保這些重要指令的執行。指令冗

- 關鍵字:

單片機 復位

- 單論單片機硬件系統設計解決方案,一般從三個方面分析:優選設計方案、增加冗余和容錯率、采用硬件抗干擾。本文詳細的介紹了優化這三個方面對單片硬件可靠性帶來的好處。

1、選優設計

在系統硬件設計和加工時,應該選用質量好的接插件,設計好工藝結構;選用合格的元器件,進行嚴格的測試、篩選和老化;設計時技術參數(如負載)要留有一定的余量或降額使用元器件;提高印制板和組裝的質量。

2、采用硬件抗干擾措施

來自供電系統以及通過導線傳輸、電磁耦合等產生的電磁干擾信號,是單片機系統工作不穩定的重要因素,在系統硬件設計時

- 關鍵字:

單片機 復位

- 異步復位相比同步復位: 1. 通常情況下(已知復位信號與時鐘的關系),最大的缺點在于異步復位導致設計變成了 ...

- 關鍵字:

同步異步 復位 亞穩態可靠性

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

嵌入式軟件 復位 初始化 向量表 ARM

- 單片機復位后,程序計數器PC的內容為0000H,所以系統必須從0000H單元開始取指令來執行程序。0000H單元是系統的 ...

- 關鍵字:

MCS-51 單片機 復位 系統

- 時鐘電路:8031單片機的時鐘信號通常用兩種電路形式得到:內部振蕩方式和外部振蕩方式。在引腳XTAL1和XTAL2外接 ...

- 關鍵字:

51單片機 時鐘 復位

- STM32軟件復位(基于庫文件V3.5), STM32軟件復位(基于庫文件V3.5)void SoftReset(void){__set_FAULTMASK(1); // 關閉所有中端NVIC_SystemReset();// 復位}在官方軟件庫的 core_cm3.h 文件里 直接提供了 系統復位的函數static __INLINE void NVIC_Sys

- 關鍵字:

文件 V3.5 基于 復位 軟件 STM32

復位介紹

您好,目前還沒有人創建詞條復位!

歡迎您創建該詞條,闡述對復位的理解,并與今后在此搜索復位的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473