SHARC處理器的起源和演進

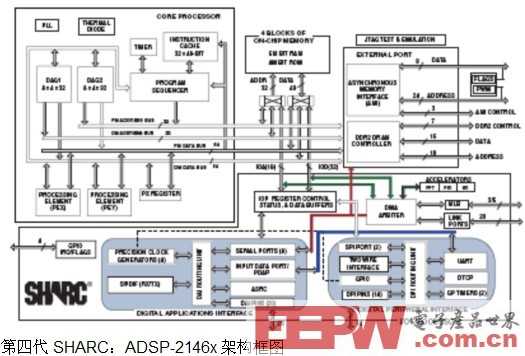

第四代SHARC系列——ADSP-2146x

本文引用地址:http://www.104case.com/article/98491.htm

第三代SHARC處理器在優(yōu)化性價比方面取得了成功,推動浮點處理器進入了對成本敏感的消費類應用,而這類應用曾被人們認為是不可能使用昂貴的浮點處理器的。

ADI公司現(xiàn)在面臨著一個有意思的挑戰(zhàn):如何進一步改進具備優(yōu)異性價比的浮點處理器?

在定義第四代處理器時,產品開發(fā)團隊注重的是核心價值,正是它們使得SHARC一直處于浮點DSP技術的前沿:

市場領先性能

架構平衡

性能可擴展性

智能集成

下面將詳細介紹上述每個關鍵的方面。

ADSP-2146x性能增強

在ADSP-2136x系列內核改進的基礎上,ADI的SHARC開發(fā)團隊制定了更高的性能目標,并采用臺積電(TSMC)的65nm硅工藝繼續(xù)優(yōu)化性能和成本平衡。通過仔細的工程設計和規(guī)劃,ADI在2008年11月正式發(fā)布了ADSP-2146x系列處理器,其內核性能可達450MHz,與最接近的競爭產品相比幾乎高出30%。然而,ADI設計團隊并不滿足于僅僅增強性能,開始尋求創(chuàng)新的方式來大幅度提高運算性能,同時對功耗和成本的影響降至最小。

許多工程師利用浮點處理器提供的寬動態(tài)范圍實現(xiàn)各種算法,如圖案檢測、數(shù)據(jù)壓縮/解壓縮、加密/解密和自適應濾波。在其中的許多運算密集型算法中,快速傅里葉變換(FFT)、有限沖擊響應(FIR)濾波器和無限沖激響應(IIR)濾波器等一些基本的信號處理單元得到了廣泛使用,并作為大多數(shù)數(shù)字信號處理應用的基礎。專注于這些內核信號處理構建模塊的ADI公司開始將這些功能集成進2146x DMA架構中,以便進一步增強SHARC內核的450MHz性能。

在簡單的編程模型基礎上,DSP工程師可以將這些“加速器”的每個看作是一個簡單的外設。每個加速器配置有自己的本地存儲器用于數(shù)據(jù)和系數(shù)存儲,從而不會增加內核處理器的開銷。另外,還有一組加速器專用寄存器用于設置加速器,包括主存儲器中的系數(shù)起始地址、計數(shù)器等信息。當設置完成后,程序就開始按順序運行,用戶只需簡單地等待表示處理結束的中斷。

評論