一種基于PCI總線和DSP技術的虛擬儀器設計

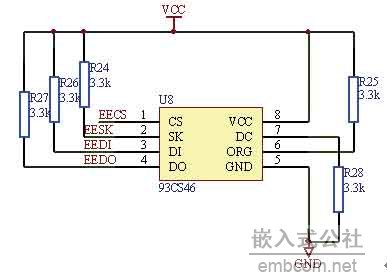

PCI分配資源的數據來源是通過外擴的EEPROM來實現的,根據PCI9052接口芯片的要求,選用Microchip公司支持三線串行接口的EEPROM。在電源上電期間,PCI的RST#信號復位PCI9052內部寄存器。而PCI9052也輸出局部復位信號(LRESET#)并檢查是否存在外部EEPROM,如果存在并且第一個16位字不是FFFFH,則PCI9052加載EEPROM中的數據到PCI9052的內部寄存器中;否則默認值被使用。PCI9052配置寄存器僅能由EEPROM或PCI主機處理器寫。在EEPROM初始化期間,PCI9052用RETRY信號來響應 PCI目標訪問。圖3給出了本設計中EEPROM(93CS46)和PCI9052的連接電路圖。

本文引用地址:http://www.104case.com/article/93522.htm

圖3 EEPROM和PCI9052的連接電路圖

EEPROM中配置的主要信息包括:設備識別號、供應商代號、四個局部總線空間的大小以及空間的基地址等。可以事先通過編程器將配置信息寫入配置EEPROM中,也可在系統啟動后用PLXMon對EEPROM進行操作。

2 系統控制邏輯的實現

由于CPLD器件掉電后可保存芯片內部程序,無須煩瑣的重復燒寫,因此本設計采用Altera公司的 CPLD器件,作為PCI接口芯片及存儲芯片的邏輯控制。考慮到需要使用局部地址/數據各16根線,控制信號線22根,還要為數據采集電路預留些I/O引腳,最后決定采用144腳TQFP封裝的EPM3128。

評論