基于XC2C64A芯片的無線錄井絞車信號檢測電路設計

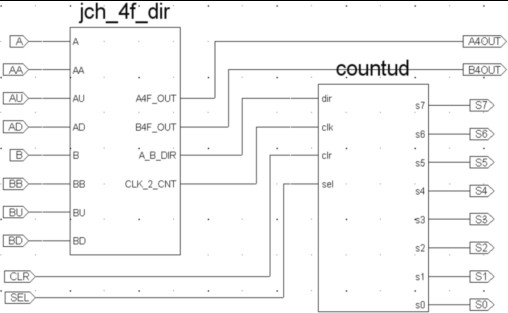

根據如上的設計原理,采用Xilinx公司的EDA軟件ISE和模塊化設計[4]的方法設計了無線錄井絞車信號的檢測電路,其頂層設計電路如圖2所示,該電路包括兩個子模塊:倍頻、鑒相子模塊jch_4f_dir,具有4倍頻和方向鑒別功能;16位二進制可控加減計數與數據接口子模塊countud,具有加/減計數(由方向鑒別信號控制)和MCU選擇讀取高/低8位計數數據等功能。該電路在XC2C64A-7VC44I器件[5]上進行了下載測試。

本文引用地址:http://www.104case.com/article/93391.htm

圖2 絞車信號四倍頻、鑒相與計數頂層電路圖

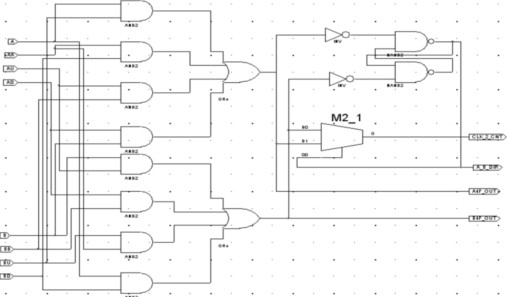

A、B、AA、BB、AU、AD、BU、BD共8路信號經過如圖3中左側所示的倍頻電路,產生4倍頻的脈沖信號,給后面的計數器提供計數時鐘信號;如圖3中右上側所示的由與非門組成的RS觸發器,是鑒相(方向鑒別)電路,可以得到反映絞車傳感器A、B兩相信號到達先后的方向信號A_B_DIR。假設絞車正轉,A超前B,A_B_DIR=1;絞車反轉, B超前A,A_B_DIR=0。

鑒相(方向)信號A_B_DIR一方面連接到二選一數據選擇器的選擇輸入端S0,用來控制A4F_OUT和B4F_OUT選通到如圖2右側所示的計數器countud進行計數,當A_B_DIR=1(A超前B)時,clk=A4F_OUT(有脈沖輸出);當A_B_DIR=0(B超前A)時clk= B4F_OUT(有脈沖輸出);同時,A_B_DIR也控制計數器進行加法(A_B_DIR=0)或減法(A_B_DIR=1)計數。

圖3絞車信號四倍頻與鑒相電路圖

16位二進制加/減計數器的主要功能設計描述如下所示(采用Verilog HDL)。其中,clk是計數時鐘輸入端,clr是異步清零端,dir是加減計數控制端:dir=1,減法計數,dir=0,加法計數;sel是計數數據讀取控制端,由單片機給出的選擇信號實現高8位、低8位的計數數據輸出,sel=0,低8位,sel=1,高8位。

無線錄井絞車倍頻、鑒相與計數電路的仿真測試

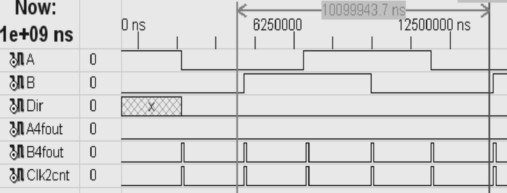

在Xilinx的ISE環境下對倍頻、鑒相子模塊jch_4f_dir的仿真波形圖示于圖4。該波形是絞車傳感器輸出B相波形超前A相波形90°時的仿真結果。此時,倍頻輸出信號B4fout與A(或B)信號的頻率成4倍關系,鑒相(方向鑒別)輸出信號Dir=0,這與前面的原理分析完全一致。

圖4 B超前A的四倍頻與鑒相輸出信號波形圖

隔離器相關文章:隔離器原理

評論