利用頻域時鐘抖動分析加快設計驗證過程(07-100)

—— 利用頻域時鐘抖動分析加快設計驗證過程

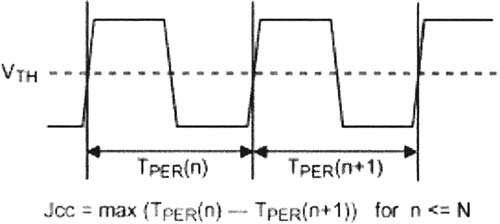

參考時鐘是最終的系統定時源。它為發射機、已分配和未分配的時鐘系統提供時基,而接收機的時鐘恢復電路可以重現參考時鐘特征。現在我們將探討時鐘抖動如何在系統發射機中進行傳輸。

發射機必須用適當的因數乘以參考時鐘獲得數據速率,才能確定邏輯變換定時。例如,對于100 MHz參考時鐘和5 Gb/s輸出信號,發射機將用PLL給參考時鐘乘以因數50。PLL乘法器不僅放大時鐘抖動,還引入其自身的抖動,主要是PLL壓控振蕩器(VCO)的RJ。頻率乘以因數n的結果是相位噪聲功率載波比乘以n2,所以抖動迅速變大。

圖2 發射機時鐘抖動的結果

發射機中的PLL乘法器具有一定的頻率響應,通常是如圖3所示的二階響應。非均勻頻率響應會產生一個值得注意的問題:時鐘抖動實際上有什么影響?如果PLL非常出色且帶寬為零,那么它將過濾掉所有的時鐘抖動,而為發射機提供無抖動時基。當然,零帶寬意味著無限鎖定時間,所以我們不得不綜合考慮,但是PLL帶寬越窄,參考時鐘加入數據中的抖動就越小。確定時鐘是否能在系統中正常工作且符合預期的BER要求,需要對抖動頻譜進行詳細測試。

評論