推動“可編程技術勢在必行”之趨勢

—— 賽靈思目標設計平臺:推動“可編程技術勢在必行”之趨勢

賽靈思發明了可插接IP(socketable IP)這一詞來表示不需要很多支持客戶就可方便使用的IP,也就是即插即用型IP。 遠在制定即插即用型IP標準之前,賽靈思早就已經在開發IP核。 然而,過去10多年,隨著IP行業逐漸成熟,擁有大型IP庫的企業開始認真考慮保存和擴展這一投資的方法。 為實現這些目標,IP行業采用的標準之一就是IP-XACT。 賽靈思也開始采用這一行業標準的IP庫格式。將 ISE Design Suite中的CORE Generator(TM)工具開放給第三方和客戶IP,從而支持設計重利用。 COREGenerator 軟件提供了用戶可定制的功能目錄。就復雜度來說,從存儲器和FIFO等通用功能,直到濾波器和變換等系統級構建模塊都有。

此外,賽靈思還采用并擴展了建議的IEEE IP Quality (QIP)標準,并將其同時用于賽靈思自己以及合作伙伴開發的IP。 作為行業領導廠商,賽靈思公司很久之前就開發并提供專有的加密技術,并且是唯一經過認證的符合美國國內政府標準的安全解決方案FPGA供應商。 現在,賽靈思正在利用其豐富的知識和經驗來幫助推動IEEE標準(IEEE Std 1735)。 一旦獲得批準,這一標準將可使賽靈思簡化IP庫中所有可插接IP(無論是誰開發的)的安全保證。

經過認證的參考設計

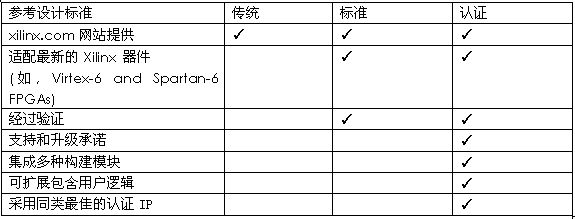

通過認證參考設計的分類方法,賽靈思與強大的第三方合作伙伴一起理順了參考設計的開發和提供過程。 認證參考設計滿足并超過標準參考設計的要求。 賽靈思將會繼續支持許多標準參考設計(參考表1),但認證參考設計將盡可能基于經過認證的IP組件。他們在目標硬件上的使用是有保證的,并且在產品生命周期內都能夠獲得支持。

這一創新的影響為多個領域提供了一個共同的起始點,可滿足不同用戶群體的要求,因此將會涉及到目標設計平臺的每一層。 這樣,新的基礎平臺將為所有領域提供更大的互操作能力并提高易用性。

統一的開發板戰略

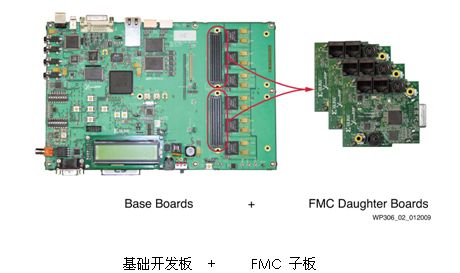

從Virtex-6 和 Spartan-6系列開始,賽靈思采用了新的統一開發板策略,使得賽靈思公司及其生態合作伙伴廠商更高效地創建標準化的互相協調的基礎開發板。 這些可擴展的靈活的基礎開發板都采用了子卡擴展的業界標準FPGA多層板(FMC)。 VITA支持的FMC (VITA 57)標準在開發時就考慮到了FPGA,并且獲得越來越多的硬件、開發板和系統廠商支持。 我們所有的基礎開發板都采用這一標準,因此為所有賽靈思目標設計平臺創造了一個統一的可擴展的板開發機制。

基礎開發板 + FMC 子板

圖 2: 卡和FPGA之間的靈活互連

推薦閱讀:

賽靈思推出Virtex-6 FPGA系列滿足高帶寬和低功耗需求

賽靈思推出Spartan-6 FPGA系列

賽靈思開啟目標設計平臺時代

編輯解讀:

FPGA是金融海嘯的一棵救命草

評論