基于FPGA的數據高速串行通信實現

1 引言

本文引用地址:http://www.104case.com/article/90807.htm在許多實際運用的場合中,數字信號傳輸具有數據量大,傳輸速度高,采用串行傳輸等特點。這就要求數據收發雙方采用合理的編解碼方式及高速器件。數字信號傳輸一般分并行傳輸、串行傳輸兩種。并行傳輸具有數據源和數據目的地物理連接方便,誤碼率低,傳輸速率高。但是并行傳輸方式要求各條線路同步,因此需要傳輸定時和控制信號,而其各路信號在經過轉發與放大處理后,將引起不同的延遲與畸變,難以實現并行同步。若采用更復雜的技術、設備與線路,其成本會顯著上升。而高速遠程數據傳輸一般采用串行同步傳輸。傳統建立準確的時鐘信號的方法是采用鎖相環技術。但鎖相環有若干個明顯缺陷,一是其同步建立時間及調整精度即使采用變階的方法也很難兼顧;二是鎖相環需要一個高精度高頻率的本地時鐘。 本文所討論的兩種串行同步傳輸方法,無需高頻率時鐘信號,就可完全數字化。采用Altera公司的ACEXlK系列器件完成電路設計,且外圍電路簡單,成本低,效果好。

2主要器件介紹

編碼和解碼采用ACEXlK系列器件EPlK100QC208-2。ACEXlK器件是Altera公司針對通信、音頻處理及類似場合應用而設計的。該系列器件具有如下特性:

高性能。采用查找表(LUT)和嵌入式陣列塊(EAB)相結合的結構,適用于實現復雜邏輯功能和存儲器功能,例如通信中應用的DSP、多通道數據處理、數據傳遞和微控制等;

高密度。典型門數為1萬到10萬門,有多達49 152位的RAM(每個EAB有4 096位RAM)。

系統性能。器件內核采用2.5 V電壓,功耗低,其多電壓引腳驅動2.5 V、3.3 V、5.0 V的器件,也可被這些電壓所驅動,雙向I/O引腳執行速度可達250 MHz;

靈活的內部互聯。具有快速連續式延時可預測的快速通道互連。

3實現方法

本文所述方法應用于數字音頻數據實時傳輸。原始數字音頻每一幀視頻數據為并行8位,速率達2 Mb/s,串行傳輸速度為16 Mb/s。

3.1新的曼徹斯編碼方法 這種方法是在接收端利用狀態轉移圖的方法得到同步時鐘信號。具體方法如下:

(1)幀同步信號的產生

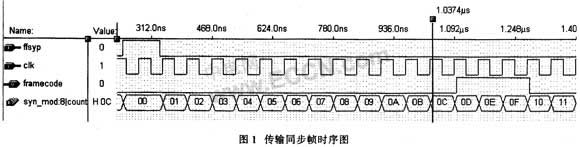

發送方系統提供64 MHz時鐘,將其4分頻得到16 MHz時鐘作為系統時鐘,64 MHz時鐘僅用于最后的消除信號毛刺。幀同步共16位,其中前12位為"0",后3位為"1",最后1位為"0"。仿真時序如圖1所示。

(2)編碼方法

數據發送采用曼徹斯特編碼,編碼規則為:0→01(零相位的一個周期的方波);1→10(π相位的一個周期的方波)。

從以上規則可知輸出信號將在每一位碼元中間產生跳變,因此可采用具有游程短,位定時信息豐富的曼徹斯特編碼電路。編碼時,當輸入信號為"0"時,輸出為時鐘的"非";當輸入信號為"1"時,輸出與時鐘一致。因此,可采用數據選擇時鐘,其電路如圖2所示。

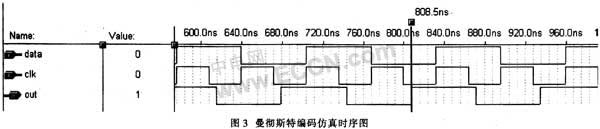

仿真的編碼時序如圖3所示,當輸人數據(data)為"1",輸出(out)與時鐘(clk)同相(稍有延時);反之,當輸入數據為"0",輸出與時鐘反相(稍有延時)。

(3)狀態轉移圖生成同步信號

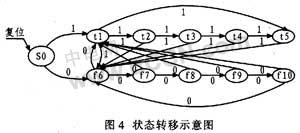

接收方系統提供80 MHz時鐘,接收方和發送方的時鐘并非來自同一個時鐘源。將發送方的信號通過序列碼檢測器,發送方的幀同步信號有一個維持187.5 ns的脈沖(3個16 MHz時鐘),當接收方檢測到"11111111111111"時(14個80 MHz時鐘,共175 ns),則認為是有效信號,然后向后級發出一個復位信號,接收方的后繼模塊開始重新工作。由于發送方采用曼徹斯特編碼,數據不會出現連續的"1"或連續的"0",游程短,這種檢測幀同步信號的方法是有效的,不存在把所要傳輸的數據當成幀同步的情況。當該復位信號產生后,狀態機開始工作,用狀態機的狀態轉移產生同步信號。狀態轉移圖如圖4所示。

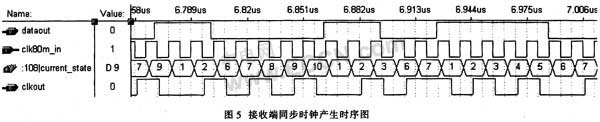

根據曼徹斯特編碼規則,每一位兩個碼元中間電平產生跳變,因此不會出現超過62.5 ns的"1"或者"0",反映在狀態轉移圖上表現為最多出現6個連續的"1"或者"0"。當出現"111111"時,根據狀態轉移圖,它將返回到狀態t1,但是下次必然轉移到狀態f6,因此對同步時鐘的輸出沒有影響。該方法仿真的波形圖如圖5所示,其中dataout為發送方的輸出信號,即接收方的輸人信號;clk80m_in為接收方的系統時鐘;current_state為狀態機的狀態,狀態0~10分別對應狀態轉移圖4的狀態S0,t1~t5,f6~f10;clkout為恢復出來的同步時鐘。當出現一個31 ns寬度的電平時將產生一個同步時鐘;當出現持續62 ns寬度的脈沖時產生兩個同步時鐘。采用clkout的上升沿即可準確恢復原信號。

由于不會連續出現超過6個"1"或"0",累積誤差小,采用該方法,對接收方時鐘精度要求不高,仿真時將時鐘分別調為80.6 MHz和79.4 MHz,在這兩種情況下都能準確得到同步時鐘并恢復原信號。與鎖相環相比,它所需的建立時間要短得多。

3.2另一種編碼方法

另一種比較特殊編碼方式含有豐富的時鐘信號。接收端將接收到的數據延時即可得到同步時鐘。其產生幀同步新的曼徹斯特編碼方法一致。

(1)編碼方法

發送方系統提供64 MHz時鐘,原始信號速率依舊為16 MHz,數據的編碼方式:0→1000,1→1110。

一個碼元對應64 MHz的4位編碼。每一個碼元開始時第1位為"1",第2和第3位為輸入信號信息,第4位是"0",這樣便可保證在每一個碼元開始時產生上升沿。該上升沿便是一個非常優良的同步時鐘,只要將上升沿對準數據的有效位置(編碼的第2,3位),即可恢復原信號。

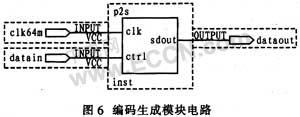

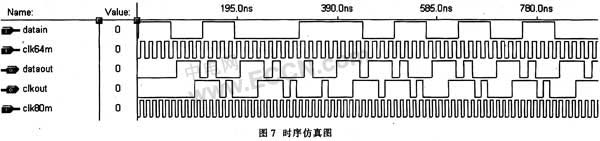

當輸入信號為"1",在延時一個碼元寬度(1/16 MHz)后,輸出"1110";當輸入信號為"0",延時一個碼元寬度(1/16 MHz)后輸出"1000"。其實質就是一個序列碼發生器,根據不同的輸入,產生不同的輸出序列。編碼電路是采用VHDL語言實現,生成模塊如圖6所示,時序仿真如圖7所示。

(2)接收端同步時鐘提取

接收方檢測幀同步的方法與新的曼徹斯特編碼方法一樣。解碼過程是將輸入信號通過D觸發器延時得到同步時鐘,再由同步時鐘恢復原信號。D觸發器的時鐘采用接收方的系統時鐘80 MHz,則通過一個D觸發器的延時時間T的范圍0~12.5 ns,可通過兩D觸發器延時時間T的范圍12.5~25 ns,通過3個觸發器延時時間T的范圍25.0~37.5 ns,這樣就可以將上升沿延時到數據編碼的有效位置(編碼第2、3位的時間范圍是15.625~46.875 ns)。當信號通過D觸發器,信號的寬度可能會有變化,這里把通過D觸發器的信號作為同步時鐘,只關心其上升沿位置,而其寬度的變化不會影響解碼過程。

圖7中datain為輸入的原信號,dataout為編碼后的信號,clkout為得到的同步時鐘,clk64m為發送方系統時鐘,clk80m為接收方系統時鐘。當輸入第1個碼元,還未產生輸出信號;輸入第2個碼元時,第1個碼元"1"所對應64 MHz編碼"1110"輸出;輸入第3個碼元時,將第2個碼元"0"所對應64 MHz編碼"1000"輸出,依次類推。在接收方,將dataout延時得到clkout,由圖可看出每次clkout的上升沿都對準編碼的有效部分,這樣就可準確的恢復原信號。

這種方法雖然編碼較為復雜,但優點也是顯而易見的,它的同步建立時間極短,解碼電路原理和設計都極其簡單,不易出錯。通過三個D觸發器延時時間T范圍25.0~37.5ns,而編碼第2、3位的時間范圍是15.625~46.875 ns。時間上存在較大冗余,只要每一位解調時誤差不超過9 ns就能準確恢復原信號,這樣的精度要求對于實際系統來說是很容易實現的。

4結語

這兩種同步方法與鎖相環相比,優點明顯,建立時間短,只需要一個幀同步用來檢測數據開始,然后就可在一個碼元時間內恢復同步時鐘,而且對接收方時鐘的精度和頻率要求不是很高,整個編碼和解碼可以分別用一個FPGA完成設計,電路設計全數字化,大大降低了PCB設計的成本和難度,且調試方便,縮短了項目周期。

fpga相關文章:fpga是什么

通信相關文章:通信原理

鎖相環相關文章:鎖相環原理

評論