基于FPGA的空間存儲器的糾錯系統

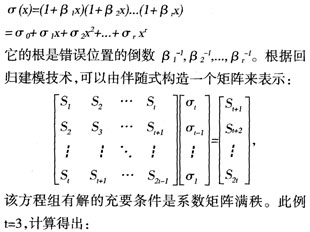

(2)系數計算電路

本文引用地址:http://www.104case.com/article/86848.htm令錯誤位置多項式

(3)錯誤位置計算

由上一步我們得出錯誤圖樣為:

因此原碼多項式為:

![]()

3、仿真與下載

對于上述編譯碼算法,采用Verilog HDL可綜合語言來描述,整個程序分為頂層模塊和底層模塊,頂層模塊很簡單,主要完成底層模塊的調用和數據的復位,編碼算法主要由底層模塊完成。其中包括編譯碼算法主程序,撥碼開關控制程序,液晶顯示程序,系統函數PLL(鎖相環)程序。系統利用兩個撥碼開關sw1,sw2來控制編碼結果或譯碼結果的下載與顯示。

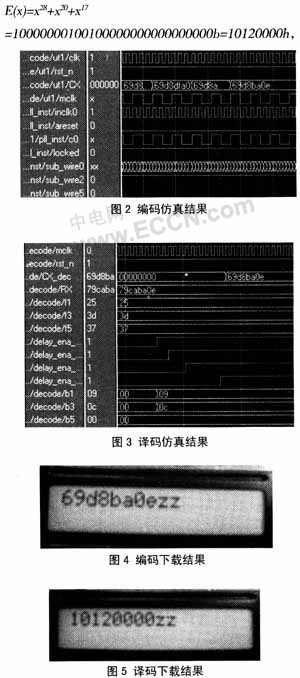

圖2和圖3是編碼和譯碼的仿真圖,仿真工具用的是modelsim 6.0,編碼結果CX=0x69d8ba0e,譯碼過程中,根據接收多項式RX=0x79caba0e以及最小多項式f1=0x25,f3=0x3d,f5=0x37,譯碼后得出錯誤多項式EX=0x10120000,最后RX與EX相與得出CX_dec=0x69d8ba0e,與原碼一致。圖4和圖5是下載后顯示到液晶屏的結果CX=0x69d8ba0e,EX=0x10120000,所用編譯工具是quartusⅡ5.0,FPGA芯片采用的是Altera Cyclone EP1C6,用到1個PLL,引腳數15個,芯片資源耗用不超過5萬門。

4、結束語

BcH(31,16)編譯碼算法,可以糾正3位錯誤,用VerilogHDL可綜合語言描述以上的編碼糾錯過程,軟件仿真和硬件下載都證明了算法的正確性和可行性。整套試驗系統是模擬空間存儲器受到高能粒子的干擾而發生錯誤,這對于我們AMS實驗也是很關鍵的一步,現階段我們用到的防護措施是三倍冗余編碼糾錯,但它占用的硬件資源比較多,而本文中所研究的循環BCH碼能夠節省資源,糾錯效果也很明顯,所以它將會在AMS項目中得到實際的應用。

評論