5/3提升小波在DM642上的實現與優化

提升小波變換不僅具有傳統小波多分辨率的優點,而且簡化了運算,便于硬件實現,因此在數字圖像編碼中得到廣泛應用。在新的圖像壓縮標準JPEG2000中,采用9/7、5/3提升小波變換作為編碼算法,其中5/3小波變換是一種可逆的整數變換,可以實現無損或有損的圖像壓縮。在通用的DSP芯片上實現該算法具有很好的可擴展性、可升級性與易維護性。用這種方式靈活性強,完全能滿足各種處理需求。

本文引用地址:http://www.104case.com/article/86067.htm1提升算法

提升算法[1]是由Sweldens等在Mallat算法的基礎上提出的,也稱為第二代小波變換。與Mallat算法相比,提升算法不依賴傅立葉變換,降低了計算量和復雜度,運行效率相應提高。由于具有整數變換及耗費存儲單元少的特點,提升算法很適合于在定點DSP上實現。

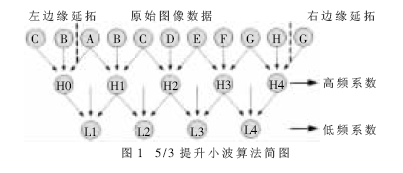

小波提升算法的基本思想是通過基本小波逐步構建出一個具有更加良好性質的新小波。其實現步驟為分解(split)、預測(predict)和更新(update)。

首先按照對原信號進行對稱延拓得到新的x(n)。

分解是將數據分為偶數序列x(2n)和奇數序列x(2n+1)二個部分;

預測是用分解的偶數序列預測奇數序列,得到的預測誤差為變換的高頻分量:H(n)=x(2n+1)-{[x(2n)+x(2n+2)]>>1}

更新是由預測誤差更新偶數序列,得到變換的低頻分量: L(n)=x(2n)+{[H(n)+H(n-1)+2]>>2}

計算過程如圖1所示。

2 基于DM642的優化策略

2.1 DM642的兩級CACHE結構

DM642是一款專門面向多媒體處理領域應用的處理器,是構建多媒體通信系統的良好平臺。它采用C64xDSP內核,片內RAM采用兩級CACHE結構[4][5],分為L1P、L1D和L2。L1只能作為CACHE被CPU訪問,均為16KB,訪問周期與CPU周期一致,其中L1P為直接映射,L1D為兩路成組相關;L2可以由程序配置為CACHE和SRAM。

2.2 改進的算法結構

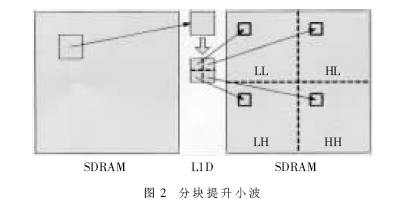

傳統的小波變換都是對整幅圖像作變換,先對每一行作變換,然后再對每一列作變換。用這種方式在DSP上實現該算法時效率比較低。因為DSP的L1D很小,只有16KB,不能緩存整幅圖像,因此原始圖像數據通常保存在速度較低的外部存儲器上。這樣CPU從L1D每讀取一行數據時必然會產生缺失,大量缺失會嚴重阻塞CPU的運行,延長程序的執行時間。為了減少缺失的發生,必須將傳統的變換進行改進。將原來對整幅圖像的變換改為分塊的變換,即每次從圖像中取出一個塊,先后完成行、列變換后再按照一定的規則保存到系數緩存中,如圖2所示。

在這種方法中,SDRAM中的一個數據塊首先傳輸到L2中,然后取到L1D中進行水平方向的提升,再對該塊進行垂直方向的提升。這樣,由于垂直提升所需的數據都在L1D中,避免了此處數據緩存缺失的產生,使總的缺失數大大降低。

2.3 數據傳輸

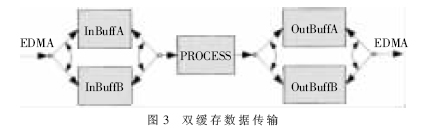

(1)SDRAM與L2間的數據傳輸

由于EDMA[6][7]數據傳輸與CPU運行相互獨立,因此在L2中開辟兩塊緩存:EDMA在CPU處理InBuffA的同時將下一塊數據傳輸到InBuffB,解決了CPU讀取低速設備SDRAM引起的時延,如圖3所示。

(2)L2與L1D間的數據傳輸

CPU首先訪問第一級CACHE中的程序和數據,如果沒有命中則訪問第二級CACHE(如果配置L2的一部分為CACHE),若還沒有命中就要訪問外部存儲空間。在這個過程中,CPU一直處于阻塞狀態,直至讀取的數據有效。所以,在對L2中的數據塊進行水平提升時,CPU讀取每一行都會產生缺失。針對這種情況,TMS320C64x系列DSP為L1D提供了一種高速緩存缺失處理的流水處理機制。若連續多次未命中,CPU等待時間就會重疊,總體上減少了平均缺失造成的CPU阻塞時間。

因此,在CPU對數據進行水平提升前,利用缺失流水技術,將當前數據塊全部讀取到L1D中,隨后再對該數據塊進行水平提升,則不會再發生缺失,并可提高運算速度。

2.4 L1P與L1D性能優化

L1D是兩路成組相關,每組8KB,總容量16KB。CPU一次處理的數據不應超過8KB,并且所有的原始數據都連續存儲在同一CACHE組中;程序的中間過程數據保留在預分配的另一個CACHE組中。

數據讀取到L1D之后,首先由8位擴展成16位,然后對這些數據進行水平提升,只要這些數據能保留在L1D中,隨后進行的垂直提升就可以完全避免缺失。因此,數據塊的大小是由中間過程數據決定的,所有中間過程數據加起來不能超過8KB,選取數據塊是32×32。

當多個函數映射到L1P的同一個CACHE行時就會引起沖突缺失,所以必須合理放置這些函數。由于實現提升的全部函數加起來不超過16KB,因此,如果能將這些函數安排在一個連續的存儲空間內,就可以完全避免由沖突引起的L1P缺失。可以在cmd[8]文件的SECTIONS中添加一個GROUP,然后將頻繁調用的函數放到GROUP中:

SECTIONS

{

GROUP > ISRAM

{

.text:_horz

.text:_vert

.text:_IMG_pix_pand

…

}…}

評論