基于多路移相時鐘的瞬時測頻模塊設計

脈沖包絡信號由檢波電路提供,作為被測信號的脈沖寬度輸入信號。若采用變閘門測頻方式,脈寬計數器對每個脈沖包絡的寬度進行測量,其脈寬值在脈沖包絡下降沿時保存,并在下一個脈沖包絡的上升沿之前提供給預閘門計數器作為預閘門計數參考值。

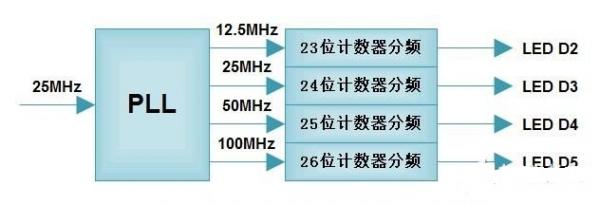

本文引用地址:http://www.104case.com/article/85982.htm該測頻方案需對連續波進行1 ms閘門時間的測量,對于400 MHz的標準時鐘信號,采用二十位同步計數器對被測信號和標準時鐘計數。二十位同步計數器的計數頻率可達416 MHz,其最大計數值為1048576,用400 MHz的標準時鐘信粵計數,對應的計數時間為2.6 ms。計數器用Quartus6.0軟件中的Mega Wizard Plug-in Manager工具包調用ALTERA公司提供的IP核自動生成。

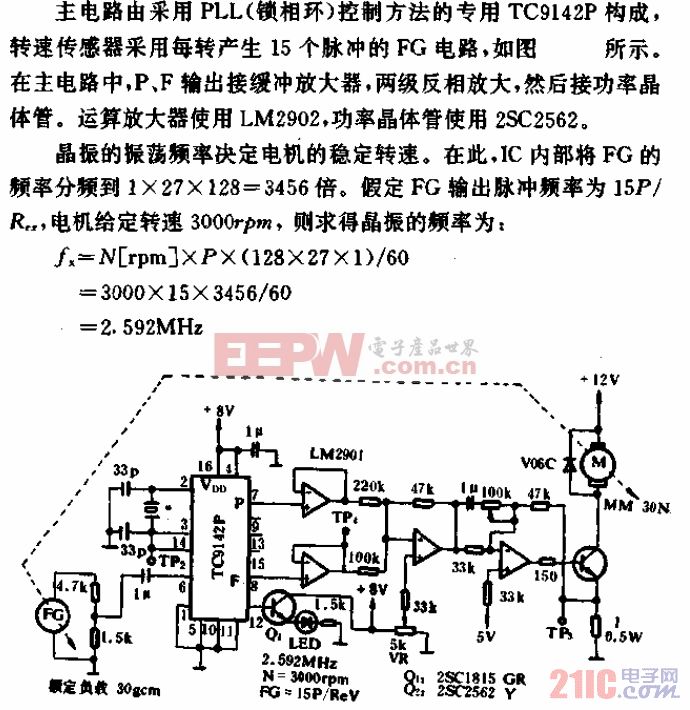

4外圍電路設計

外圍電路包括為FPGA提供標準10 MHz時鐘的恒溫晶振電路;對輸入信號進行放大、整形處理的整形電路;脈沖包絡檢測電路以及為整個模塊提供-5 V、+1.2 V、+3.3 V、+5 V電壓的電源電路。

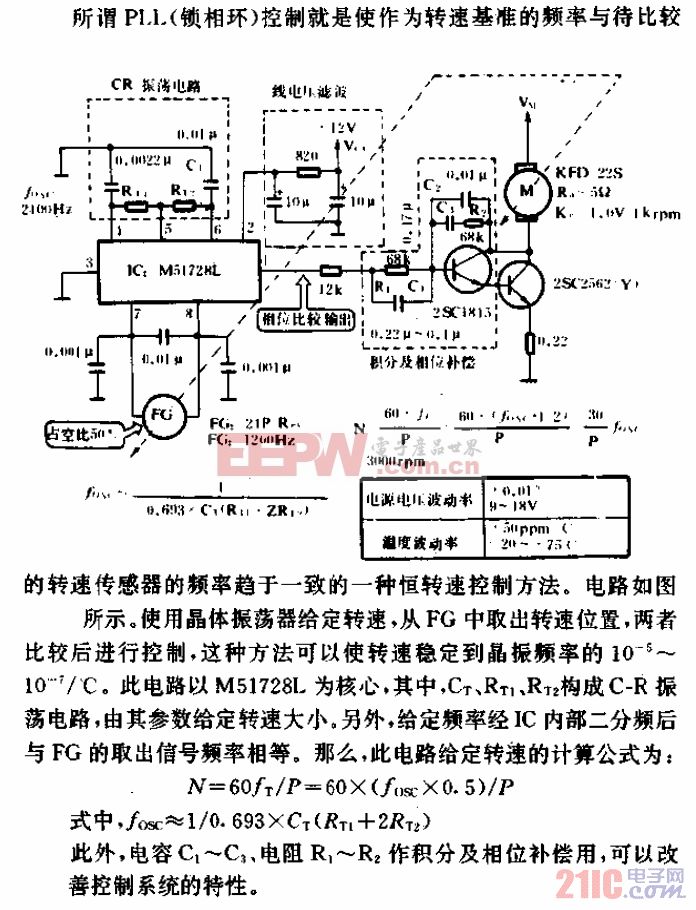

本課題測頻精度要求為±10-6,振蕩器的頻率精度至少要達到±10-7,只能選用壓控恒溫晶體振蕩器構建標準頻率源。本課題所用晶振為成都星華公司產品,通過儀器內部自帶的Allan方差測試軟件得到OCXO的秒穩在3.3×10-12,100 s的短穩在4.4×10-12。

信號接收機傳送來的被測信號振幅通常只有毫伏量級,而FPGA的輸入端口一般為LVTTL電平,故需要將輸入信號進行電平轉換。FPGA的LVTTL電平格式輸入端口的最高頻率達到200 MHz,為了能和該頻率值相配合,不形成速度瓶頸,采用超高速ECL電平輸出比較器ADC-MP563完成信號整形功能,串接電平轉換器MC100EPT25完成差分ECL電平到LVTTL邏輯電平的轉換。

脈沖包絡檢測電路檢測被測信號的包絡線,用于測量脈沖寬度。采用AD公司檢波芯片AD8310構建檢波電路,對被測信號的檢波采用單端輸入的方式。上位機用CV18.0構建人機界面。

5仿真結果說明

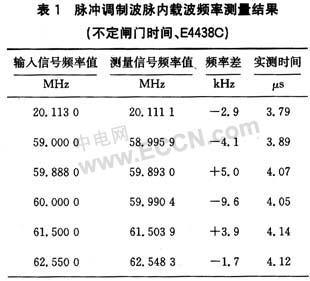

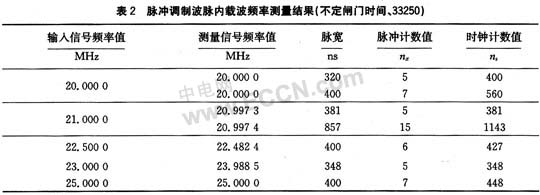

測試方法:分別用Agilent公司矢量信號發生器E4438C和任意波形發生器33250輸出信號作為被測對象,用該測頻模塊對其信號頻率進行測量,各計數值通過單片機串口上傳到上位機處理軟件,該軟件通過程序實現式(2)的算法,計算測量頻率值。測量結果如表1所示。

表1為不定脈寬脈內載波頻率測量,閘門時間根據測量開始后第一個脈沖包絡的脈寬測量值確定,由于E4438C在產生4μs脈寬時波動較大,故在某些頻點實際閘門時間偏差較大。實驗表明:系統對脈沖調制波載波測頻,在不定脈寬(4μs左右)狀態下對中頻的測頻精度優于±10 kHz。

表2為不定脈寬脈內載波頻率測量。頻率源為Agilent公司的任意波形發生器33250。實驗表明:系統對脈沖調制波載波測頻,在不定脈寬(≤400 ns)狀態下對中頻的測頻精度優

于±30 kHz。

6結束語

本文所提出的基于多路移相時鐘的等精度瞬時測頻模塊具有電路簡單,性價比高的特點,可用于捷變頻脈沖調制雷達脈內測頻。最為核心的測頻電路完全在FPGA內部構建,輸入的標準時鐘僅為10 MHz,不僅減小了布線和制板的難度,而且大幅提高了模塊的抗干擾能力保證了測量精度。整個測頻模塊用一塊板卡實現,通過測試達到預期效果,證明該設計方案具有很高的實用性。

評論