影響FPGA設(shè)計中時鐘因素的探討

總結(jié):提高工作頻率的本質(zhì)就是要減少寄存器到寄存器的時延,最有效的方法就是 避免出現(xiàn)大的組合邏輯,也就是要盡量去滿足四輸入的條件,減少LUT級聯(lián)的數(shù)量。我們 可以通過加約束、流水、切割狀態(tài)的方法提高工作頻率。

本文引用地址:http://www.104case.com/article/85938.htm在FPGA中進(jìn)行時鐘設(shè)計時也要注意一下幾點(diǎn):

1. 一個模塊盡量只用一個時鐘,這里的一個模塊是指一個module或者是一個entity。在多時鐘域的設(shè)計中涉及到跨時鐘域的設(shè)計中最好有專門一個模塊做時鐘域的隔 離。這樣做可以讓綜合器綜合出更優(yōu)的結(jié)果。

2. 除非是低功耗設(shè)計,不然不要用門控時鐘--這會增加設(shè)計的不穩(wěn)定性,在要用到門控時鐘的地方,也要將門控信號用時鐘的下降沿 打一拍再輸出與時鐘相與。

3. 禁止用計數(shù)器分頻后的信號做其它模塊的時鐘,而要用改成時鐘使能的方式,否則這種時鐘滿天飛的方式對設(shè)計的可靠性極為不利,也大大增加了靜態(tài)時序分析的復(fù)雜性。

1.4 不同時鐘域之間的同步

當(dāng)一個設(shè)計中的兩個模塊分別用的是兩個工作時鐘,那么在它們的接口處就工作在異步模式,這時為了保證數(shù)據(jù)能正確的處理那么就要對兩個模塊進(jìn)行同步。

這里的不同的時鐘域通常是以下的兩種情況:

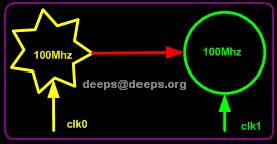

1、 兩個時鐘的頻率不同;

2、 雖然兩個時鐘的頻率相同,但是它們是兩個獨(dú)立的時鐘,其相位沒有任何關(guān)系。

分別如下兩個圖所示:

圖10 兩個時鐘的頻率完全不同

圖11兩個時鐘的頻率相同,但相位不相關(guān)

兩個時鐘域之間傳輸?shù)臄?shù)據(jù)根據(jù)不同的位寬通常采用不同的同步的方法。

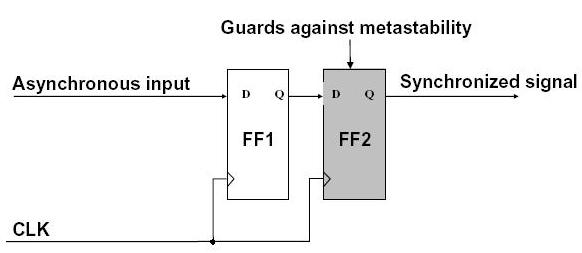

1、單bit之間的同步且發(fā)送的每個pulse至少有1個周期寬度的情況

這類同步主要是用于一些控制信號自己的同步。通常的采用方法就是輸出數(shù)據(jù)在接收的模塊中利用兩個觸發(fā)器采用系統(tǒng)時鐘打兩拍,如下圖12所示。對于這種同步需要說明以下幾點(diǎn)。

圖12 一位同步器設(shè)計

(1)圖12中的同步電路其實叫"一位同步器",它只能用來對一位異步信號進(jìn)行同步,而且這個信號的寬度必須大于本級時鐘的脈沖寬度,否則有可能根本采不到這個異步信號。

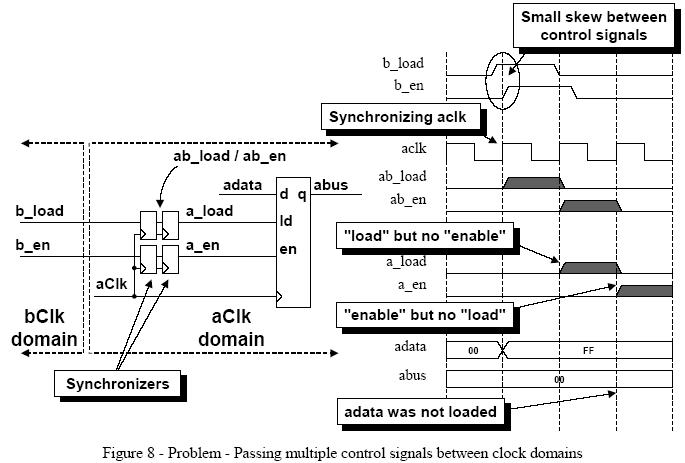

(2)為什么圖一中的同步電路只能用來對一位異步信號進(jìn)行同步呢? (a)當(dāng)有兩個或更多的異步信號(控制或地址)同時進(jìn)入本時域來控制本時域的電路時,如果這些信號分別都用圖12中的同步電路來同步就會出現(xiàn)問題,由于連線延遲或其他延遲使兩個或更多的異步信號(控制或地址)之間產(chǎn)生了skew,那么這個skew經(jīng)過圖12的同步器同步進(jìn)入本時域后,會產(chǎn)生很大的skew 或產(chǎn)生競爭,導(dǎo)致本時域電路出錯。

出現(xiàn)的問題如下圖13所示:

圖13 同步多個控制信號時出錯

(b)如果是異步數(shù)據(jù)總線要進(jìn)入本時域,同樣不能用圖12的電路,因為數(shù)據(jù)的變化是很隨機(jī)的,其0的寬度或1的寬度和本時域時鐘脈沖無關(guān),所以圖12的電路可能會采不到正確數(shù)據(jù)。

(3)注意,第二個觸發(fā)器并不是避免“亞穩(wěn)態(tài)的發(fā)生”,確切的說,該電路能夠防止亞穩(wěn)態(tài)的傳播。也就是說,一旦第一個觸發(fā)器發(fā)生了亞穩(wěn)態(tài)(可能性存在),由于有了第二個觸發(fā)器,亞穩(wěn)態(tài)不會傳播到第二個觸發(fā)器以后的電路中去。

(4)第一級觸發(fā)器發(fā)生了亞穩(wěn)態(tài),需要一個恢復(fù)時間來穩(wěn)定下來,或者叫退出亞穩(wěn)態(tài)。當(dāng)恢復(fù)時間加上第二級觸發(fā)器的建立時間(更精確的,還要減去clock skew)小于等于時鐘周期的時候(這個條件還是很容易滿足的,一般要求兩級觸發(fā)器盡量接近,中間沒有任何組合邏輯,時鐘的skew較小),第二級觸發(fā)器就可以穩(wěn)定的采樣,得到穩(wěn)定的確定的數(shù)據(jù)了,防止了亞穩(wěn)態(tài)的傳播。

(5)FF2是采樣了FF1的輸出,當(dāng)然是FF1輸出什么,F(xiàn)F2就輸出什么。僅僅延遲了1個周期。注意,亞穩(wěn)態(tài)之所以叫做亞穩(wěn)態(tài),是指一旦FF1進(jìn)入,其輸出電平不定,可能正確也可能錯誤。所以必須說明的是,雖然這種方法可以防止亞穩(wěn)態(tài)的傳播,但是并不能保證兩級觸發(fā)器之后的數(shù)據(jù)是正確的,因此,這種電路都有一定數(shù)量的錯誤電平數(shù)據(jù),所以,僅適用于少量對于錯誤不敏感的地方。對于敏感的電路,可以采用雙口RAM或FIFO。

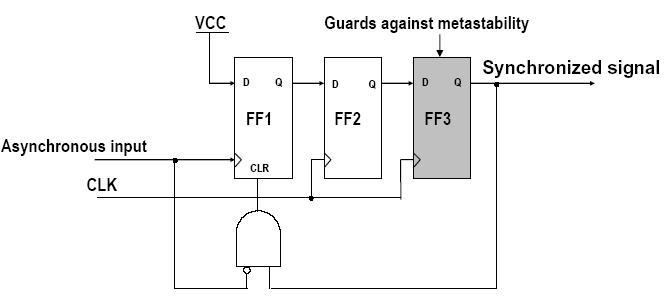

2 輸入pulse有可能小于一個時鐘周期寬度情況下的同步電路

對2的情況通常采用如下圖14的反饋電路。該電路的分析如下:假設(shè)輸入的數(shù)據(jù)是高電平,那么由于第一個觸發(fā)器FF1是高電平清零,所有輸出也是高電平,采用正確。如果輸入是第電平那么被FF1被強(qiáng)制清零,這個時候輸出位零。這樣就保證了輸出的正確性。

圖14輸入pulse有可能小于一個時鐘周期寬度情況下的同步電路

對于要控制多個信號的情況可以參考詳細(xì)的分析:www.fpga.com.cn中的設(shè)計異步多時鐘系統(tǒng)的綜合以及描述技巧.pdf。

評論