基于DSP的圖象采集與處理系統的設計

0 引言

本文引用地址:http://www.104case.com/article/85729.htm圖像處理系統的一個關鍵問題就是數據量龐大,數據處理相關性高,實時實現比較困難。即使采用高速單片機也無法滿足實時處理的需求,而DSP芯片則具有速度快,信號處理功能強大,實時性好等特點,因此,將DSP用于圖像處理可使這一難題得到較好的解決。

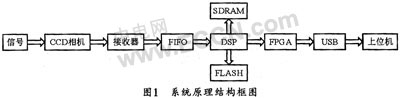

1 系統構成

本系統采用基于CameraLink接口的圖像輸出相機。DSP采用TI的TMS320C6711,這是一種高性能DSP處理器,其工作頻率為150 MHz,最大處理能力高達900MFLOps,該DSP既可滿足高速處理要求,又可滿足高精度運算時的浮點要求。

本圖像處理系統主要包括圖像采集模塊(由MDR26連接器DS90CR288A和IDT72V283組成)、圖像處理模塊(由DSP器件TMS320C6711、SDRAM圖像存儲器和FLASH程序存儲器等組成)以及圖像輸出系統(USB和FPGA)等。該系統的構成原理框圖如圖1所示。其基本工作過程是將高速CCD相機采集到的圖像數據通過電纜接入MDR26連接器,然后再接入LVDS線路接收器DS90CR288A以將其恢復成并行TTL信號,同時分離出8位圖像數據和3個控制信號。而同步FIFO作為數據緩存則不會造成數據的丟失。當其數據達到半滿時,HF有效,此時可觸發DSP中斷以通知DSP將FIFO中的數據取走,并開始進行數據處理。DSP與USB的數據傳遞建立在消息和中斷信號基礎上,當DSP或USB任何一方有數據發送時,發送方先將數據和消息送到FPGA,然后用I/O腳觸發中斷至接收方,接收方接到中斷后再到FPGA中讀取消息,然后根據消息的內容讀取數據。

本系統設計充分利用了TMS320C6711中EDMA的優勢,并用EDMA來進行整個系統的數據傳輸。由于EDMA可以進行背景操作,因而其整個采樣和輸出過程基本不影響操作。同時,也利用了TMS320C6711的二級緩存結構,再加上系統外圍采用高速的數據存儲器芯片,因而大大提高了整個系統的處理速度。

2 圖像采集與處理

2.1 Camera Link技術

Camera Link技術的核心是美國NS(NationalSemiconductor)提出的一種高速數據傳輸方法—Channel Link傳輸方法技術,該技術主要用于數字圖像數據的高速傳輸。該技術采用LVDS信號模式,但比先前的RS644傳輸方法具有明顯的優點。LVDS(Low Voltage Differential Signaling)是最近發展起來的一種利用低電壓差分信號模式的傳輸技術。LVDS信號是以+1.2 V為基準的300 mV差分形式,其低電壓擺幅差分模式具有高速傳輸數據時交叉干擾小,EMI干擾小等特點。ChannelLink采用LVDS方式傳輸數據,它將28位數據轉換成串行方式在4對線路上進行傳輸,然后再用另外一對線路傳輸時鐘信號,其最高傳輸率可達2.38 Gb/s。傳輸距離可達10 m。NS的LVDS發送器DS90CR287可用于完成并行TTL/CMOS信號到LVDS信號的轉換,LVDS線路接收器DS90CR288則用來將LVDS信號還原成并行TTL/CMOS信號。

2.2 TMS320C6711 DSK簡介

本系統采用美國TI公司的TMS320C6711DSK(DSP Starter Kit)開發工具。這是由TI公司提供的一套獨立的C6000開發實驗平臺,這種開發工具集成了一些基本的應用電路,它既可以幫助用戶評估和開發C6000系列DSP的功能,也可以作為DSP初學者的學習工具。它的硬件由6711 DSP構成,主頻為150 MHz,憑借其二級高速緩存及VLIW (very long instruction word)架構,每秒可執行900萬次浮點運算(MFLOPS)。DSK可以提供雙時鐘,通過設定可使CPU工作在150 MHz,而使擴展存儲器接口(EMIF)工作在100 MHz。 DSK上設計有16 M字節/100 MHz的SDRAM和128 K字節的ROM。SDRAM由TMS320C6711為其產生所需的控制信號和刷新信號。最大刷新周期可達15.625 ms。HPI接口可通過并口連接所有的DSP存儲空間,并有子卡接口所需的存儲器和外圍連接接口及嵌入式JTAG仿真功能。

2.3 圖像采集與處理接口設計

根據CameraLink標準,CCD輸出圖像數據經Camera link后,可由LVDS線路接收器DS90CR288將其恢復成并行的TTL/CMOS信號,并分離出8位圖像數據和3個控制信號(LVAL,DVAL,STROBE)接人同步FIFO(IDT72V283),再通過DSP的外部存儲器接口(EMIF)接入TMS320C6711DSK開發板進行圖像數據處理。其具體的圖像采集電路原理圖如圖2所示。

3 圖像輸出系統

3.1 USB芯片AN2131QC

USB芯片選用CYPRESS半導體公司的EZUSB(AN2131QC)芯片,AN2131 QC具有一個USB接口、8位數據線和16位地址線,以及3個8位I/O端口,其片內帶有增強型8051核,該8051核與傳統8051的區別在于其速度較快。傳統的8051標準指令周期是12個CLOCK,而在這里只需要4個CLOCK,因而大大提高了指令執行的時間。由于其帶有增強8051核,故可以將固件儲存在主機上,每次上電時,再將固件調用到芯片的RAM存儲器單元,這樣可使固件升級非常容易。另外,CYPRESS公司還提供了一個不需要修改就可以使用的驅動程序ezusb.Sys,這個驅動程序允許任何傳輸類型與EZ-USB芯片構建的系統進行通信。CPU的時鐘頻率為24 MHz,使用RAM作為程序存貯器,其8051程序代碼及設備描述表可以每次從主機中下載。

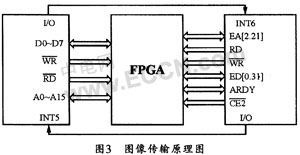

3.2 圖像輸出接口設計

TMS320C6711與AN2131QC采用并口方式進行通訊。DSP為32位處理器,其并行接口數據線為32根,而AN213 I QC的并行口為8位,若將DSP32根數據線中的8根數據線直接與USB并口相連,則DSP傳送一個32位數據需進行4次操作,這顯然會影響系統的效率。因此,可采用8位/32位數據線轉換和數據緩沖設備來將兩者相連。考慮到性能價格等因素,本設計采用FPGA作為兩者之間的緩沖設備,實現從DSP到USB數據傳輸緩沖以及32位數據線轉8位數據線功能。FPGA采用X ilinx公司SpartanIIE系列的XC2SSOE芯片作為轉換器。其圖像傳輸電路原理圖如圖3所示。

評論