利用Allegro實現嵌入式系統高速電路布線設計

1 引言

本文引用地址:http://www.104case.com/article/85065.htm隨著嵌入式微處理器主頻的不斷提高,信號的傳輸處理速度越來越快,當系統時鐘頻率達到100MHZ以上,傳統的電路設計方法和軟件已無法滿足高速電路設計的要求。在高速電路設計中,走線的等長、關鍵信號的阻抗控制、差分走線的設置等越來越重要。筆者所在的武漢華中科技大學與武漢中科院巖土力學所智能儀器室合作.以ARM9微處理器EP9315為核心的嵌入式系統完成工程檢測儀的開發。其中在該嵌入式系統硬件電路設計中的SDRAM和IDE等長走線、關鍵信號的阻抗控制和差分走線是本文的重點,同時以cirrus logic公司的網絡物理層接13芯片cs8952為例詳細介紹了網絡部分的硬件電路設計,為同類高速硬件電路設計提供了一種可借鑒的方法。

2 硬件平臺

2.1主要芯片

本設計采用的嵌入式微處理器是Cirrus Logic公司2004年7月推出的EP93XX系列中的高端產品EP9315。該微處理器是高度集成的片上系統處理器,擁有200兆赫工作頻率的 ARM920T內核,它具有ARM920T內核所有的優異性能,其中豐富的集成外設接口包括PCMCIA、接口圖形加速器、可接兩組設備的EIDE、 1/10/100Mbps以太網MAC、3個2.0全速HOST USB、專用SDRAM通道的LCD接口、觸摸屏接口、SPI串行外設接口、AC97接口、6通道I2S接口和8*8鍵盤掃描接口.并且支持4組32位 SDRAM的無縫連接等。

主芯片豐富的外設接口大大簡化了系統硬件電路.除了網絡控制部分配合使用Cirrus Logic公司的100Base—X/10Base-T物理層(PHY)接口芯片CS8952外,其他功能模塊無需增加額外的控制芯片。

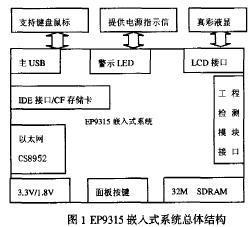

2.2系統主體結構

由圖1可見.系統以微處理器EP9315為核心,具有完備的外設接口功能,同時控制工程檢測儀。IDE/CF卡接口為工程檢測數據提供大容量移動存儲設備;擴展32M的SDRAM作為外部數據存儲空間;3個主動USB接口支持USB鍵盤鼠標;LCD接口支持STN/TFT液晶和觸摸屏.為用戶提供友好的交互界面;1/10/100 Mbps以太網為調試操作系統時下載內核及工程檢測時遠程監控提供途徑;面板按鍵為工程人員野外作業無法使用鍵盤鼠標時提供人機交互接口。

EP9315在操作系統下主頻達到200M,總線頻率100M,外設時鐘為50M,數據線和地址線的布線密度大,速度高,網絡部分對差分線和微帶線控制有特殊要求。以往使用Protel設計主要依照經驗進行PCB布局布線,顯然這種方法無法滿足當前的高速電路設計。CADENCE公司作為EDA領域最大的公司之一,其PCB設計工具性能上的優勢在高速電路設計中越來越明顯,故筆者使用CADENCE公司的PCB設計布局軟件Allegro完成高速電路設計。

3 設計實現

3.1 SDRAM的布線規則

該嵌入式系統使用64M字節的SDRAM擴展數據存儲區,由兩片K4S561632組成工作在32位模式下。最高頻率可達100M以上,對于SDRAM的數據線、時鐘線、片選及其它控制信號需要進行線長匹配,由此提出以下布線要求:

1. SDRAM 時鐘信號:時鐘信號頻率較高,為避免傳輸線效應,按照工作頻率達到或超過75MHz時布線長度應在1000mil以內的原則及為避免與相鄰信號產生串擾。走線長度不超過1000mil,線寬10mil,內部間距5mil,外部間距30mil,要求差分布線,精確匹配差分對走線。誤差允許在20mil以內。

2. 地址,片選及其它控制信號:線寬5mil,外部間距12mil,內部間距10mil。盡量走成菊花鏈拓補。可有效控制高次諧波干擾,可比時鐘線長,但不能短。

3. SDRAM數據線:線寬5mil,內部間距5mil,外部間距8mil,盡量在同一層布線,數據線與時鐘線的線長差控制在50mil內。

根據布線要求,在Allegro中設置不同的約束:針對線寬設置3 個約束SDRAM_CLK,SDRAM_ADDDR,SDRAM_DATA,設置完約束后將約束添加到對應的net上。使得各個net都具有線寬、線距約束屬性。最后為不同的信號組選擇合適的約束即可。但是設置的約束在系統CPU內部是無法達到的。因為EP9315為BGA封裝。pin間距1.27毫米,顯然在CPU內部,線寬線距無法達到上述要求,利用Allegro設置CPU特殊走線區域cpu_area。并加上area屬性,在此區域中另設置適合 BGA內部走線的約束。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)DIY機械鍵盤相關社區:機械鍵盤DIY

評論