基于PCI Express總線的R-D算法實時成像系統設計

2.3 支持PCI Express總線的接口芯片

本文引用地址:http://www.104case.com/article/84921.htm設計信號處理板卡時,為了簡化板卡,提高硬件的靈活性,這里用FPGA來控制整個板卡,包括對DSP的控制、數據交換模塊的設計以及接口的實現。事實上,在SAR處理中還經常用FPGA作方位向的預濾波、距離壓縮等工作,所以要選用資源豐富的,速度較快的,RAM容量較大的FPGA。Altera公司推出的Stratix II GX系列完全可以勝任上述工作,其內嵌的RAM可以作為本級FIFO使用,使設計更緊湊、靈活,此外還可以對其編程實現PCI Express與局部端的通信。綜合考慮,FPGA采用Altera公司的EP2SGX60E芯片。

Stratix II GX FPGA收發器工作速率為622 Mb/s~6.375 Gb/s。經過優化,FPGA能提供優異的信號完整性,降低了布板風險。在Stratix II GX器件中,收發器模塊含有特定的硬件知識產權(IP),支持多種主要協議,包括PCI Express等,還可提供低功耗解決方案,特別適合散熱困難的背板應用。設計中采用這個芯片,在很大程度上簡化了板卡結構,提高了板卡的靈活性。

3實時成像系統方案設計

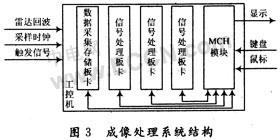

這里所設計的實時雷達成像處理系統由標準機箱、采集/存儲板卡以及信號處理板卡組成。標準機箱是板卡的支撐平臺并進行圖像的顯示。采集/存儲板卡高度集成,實現雷達回波的實時采樣和實時存儲。基于4片ADSP-TS201的信號處理板卡是成像處理的核心,4片DSP采用并行、流水的方式以達到實時成像處理的要求。采用PCIExpress總線能夠有效地利用PC機資源和應用軟件,利于開發圖形化操作界面,極大地方便了信號處理系統的調試、狀態監控以及圖像顯示。AD采樣的數據一邊存入FLASH陣列,一邊傳給DSP進行實時處理,處理完的結果通過PCI Express總線讀入計算機內存并進行顯示。信號處理板卡是專門為雷達成像設計的一種通用處理模塊。4片DSP峰值并行處理可達到12 GFLOPS的運算(DSP內核工作在500 MHz)。實際中根據算法的復雜度選取信號處理板卡的數量。成像處理系統結構如圖3所示,其中MCH模塊用來控制板間通信。

3.1數據的采集與存儲

采集/存儲板卡設計時將采集和存儲集成在一塊板卡上,可以設計成高速和低速兩種采集/存儲卡。高速卡適合于對高速的中頻采樣,如直接對高分辨SAR雷達中頻回波采樣;低速卡適合于精度要求高、速度要求低一點的場合,如在ISAR的Dechirp后以及普通的SAR基帶回波采樣。采樣后的數據經FPGA控制存人FLASH陣列。板卡上有128 GB容量的FLASH陣列,通過72片FLASH芯片并行操作(其中64片FLASH用來存儲數據,8片FLASH用來提供冗余校驗,這樣即使有幾個芯片損壞也可以保證數據的完整性),可以實現240 MB的穩定連續讀寫速度,可應用于高速大容量存儲的場合。板卡采用標準PCI Express接口,主機可以直接讀取采樣數據并進行顯示。

3.2信號處理模塊

信號處理模塊是系統的核心,由于成像算法的復雜性,選用AD公司的ADSP-TS201作為主處理器。這是一款極高性能的靜態超標量處理器,他將非常寬的存儲器寬度和雙運算模塊組合在一起。TigerSHARC靜態超標量結構使DSP每周期執行多達4條指令、24個16位定點運算和6個浮點運算。運行在500 MHz時,TS201可提供48億次40位的MAC運算或者12億次的80位MAC運算。TS201的鏈路口時鐘和數據線采用低壓差分信號,可以達到很高的速度,單個鏈路口全雙工工作的速度可以達到1 GB/s。TS201有豐富的內部存儲資源,能提供33.6GB/s的內存帶寬,特別適合并行組成高速并行處理器。從多片互連來看,他除了有完善的總線仲裁機制外還有4個高速鏈路口,可以以各種拓撲結構互連DSP,滿足大運算量的要求。

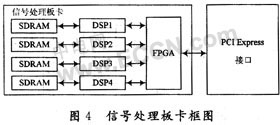

根據R-D算法既是并行的又是流水的特點,這里設計了分布式的并行系統。板卡擁有4片TS201,1 GB的存儲空間。4個DSP采用分離總線的形式與一片FPGA相連,每個DSP都有獨立的256 MB、64位寬度的SDRAM,4個DSP可以同時訪問自己的SDRAM。系統采用標準的PCI Express總線。板卡上的FPGA負責整個板子的控制和接口工作。內核工作在500 MHz時,板卡的峰值運算能力達到每秒120億次浮點運算。圖4為信號處理板卡的框圖。

4個DSP分布式互連,可以通過鏈路口進行數據交換,也可以通過FPGA進行數據傳輸。鏈路口是全雙工的,可以穩定工作在500 MHz的時鐘頻率下。每個DSP的64位數據總線連到FPGA,在FPGA中設計了交換電路,任意兩個DSP之間的數據交換速度為800 MB/s。DSP之間的鏈路口兩兩互連。

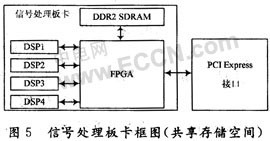

另外我們也設計了共享存儲空間的信號處理板卡,存儲器采用DDR2 SDRAM,由FPGA控制,容量為2 GB,時鐘266 MHz,由于采用雙倍數據率,單個數據線傳輸速率最高可達533 Mb/s,64位數據線的傳輸率最高4 200 MB/s。各個DSP總線都連接到FPGA上,DSP的外部時鐘為100 MHz,64位總線的數據傳輸率可達800 MB/s,4個DSP同時訪問時速度為3 200 MB/s。DSP通過FPGA來訪問存儲空間,當多個DSP同時訪問時,在FPGA內部控制訪問順序。4個DSP的鏈路口仍是兩兩互連,結構如圖5所示。

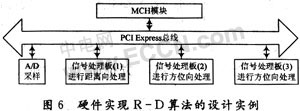

我們根據R-D算法的特點利用多處理器并行結構設計了體積小、功耗低、效率高的信號處理機。采用子孔徑方法進行距離向處理,在第一個子孔徑完成距離向處理后就可以開始數據轉置,所以距離向處理可以按子孔徑來進行流水處理,數據轉置可以與之同時進行。為了實現整體的流水作業,距離向處理和方位向處理應該在不同的運算模塊中進行,這樣在對前幅圖像進行方位向處理時,可以對下幅圖像進行距離壓縮和數據轉置。

由于方位向處理時會涉及到數據的重復利用,而且方位向的參數估計比距離向的參數估計復雜,所以方位向處理板卡數目多于距離向處理板。在這里我們用三個信號處理板卡按照流水方式實現R-D算法,第一個板卡處理距離向數據,另外兩個板卡進行方位向處理。采集存儲板卡通過PCI Express接口將采集到的數據按方位的先后傳輸給第一個信號處理板進行距離向處理,這時在板卡內部數據以回波到達順序分別進入不同的DSP,4個DSP同時接收數據并發進行處理,處理完的數據按照方位向存儲到各自的SDRAM,另外兩個板卡通過PCI Express接口接收距離向處理后的數據并發進行方位向處理,與此同時,第一個板卡進行下一幅圖像的距離向處理。每個板卡上DSP之間的數據傳輸通過鏈路口進行,由于進行數據處理時往往需要一部分樣本,鏈路口完全能夠勝任這個量級的數據通信。所有的數據均通過PCI Express總線由MCH控制傳輸方向和進行數據交換,結構如圖6所示。

5 結語

本文針對R-D SAR成像算法的特點設計了一種基于PCI Express總線的實時成像系統,該系統采用PCI Express串行總線體系結構,提高了系統的總線帶寬和總線接口的可伸縮能力,實現了數據采集和大容量實時存儲,并且具有極強的運算能力和良好的通信能力,特別適合于復雜的實時成像雷達信號處理。未來的雷達成像將進行更復雜的處理,對實時處理機的要求更高,另外彈載、星載實時成像技術的發展對成像處理機的適用環境、可靠性和穩定性提出了更高的要求,這些都需要不斷地研究與改進。

評論