SVPWM信號發生器的VHDL實現

以A相橋臂為例(另外兩相橋臂的控制方法與A相橋臂類似),狀態機進程啟動后,基準計數器開始計時,比較器實時比較計數器當前值和比較器內部預存的時間。計數器的一個工作周期可以分為三個階段:

本文引用地址:http://www.104case.com/article/82816.htm1)計數器當前值小于輸入時間TIME1_A時.狀態機處于"00"態.A相上橋臂輸出為'1';

2)計數器當前值大于等于輸入時間TIME1_A而小于TIME1_A與TIME0_A的和時,狀態機處于"01"態,A相上橋臂輸出為'0';

3)計數器當前值大于等于TIME1_A與TIME0_A的和時,狀態機處于"10"態,A相上橋臂輸出為'1'。

如果狀態機處于非法狀態"11",則圖2中管腳A和NOTA輸出為高阻態。

仿真結果

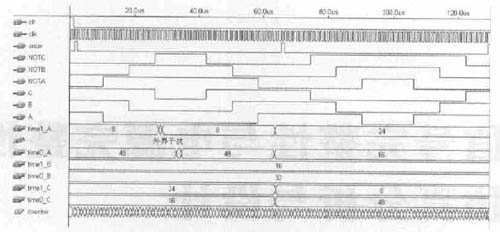

利用MAX+PLUS II軟件對本設計的邏輯功能進行仿真驗證,仿真時間為0~120us,時鐘頻率為1MHz。

采用EPM3256ATC144-7FPGA芯片進行邏輯編程后,共占用166個邏輯單元,芯片利用率為64%,具有較大的擴展空間。仿真結果如圖4所示。

圖4中輸出信號A和NOTA,B和和NOTB,C和NOTC分別代表橋式電路3組互補開關的驅動命令,輸入信號time1_A、time1_B、time1_C和time0_A,time0_B、time0_C分別代表各開關高低電平狀態的保持時間。通過仿真波形可以看到,FPGA實現了空間矢量的轉換,開關的狀態保持時間取決于輸入信號time0_A、time0_B、time0_C和time1_A、time1_B、time1_C,完全實現了時間信號到觸發信號的轉換。而且,A相橋臂有效地抵抗了外界干擾,沒有受到輸入時間信號突變的影響,表明SVPWM信號發生器具有良好的抗干擾能力。

結語

本文用VHDL硬件描述語言設計了一種由鎖存器陣列和有限狀態機構成的SVPWM信號發生器,該信號發生器不僅成功實現了輸入時間信號到SVPWM觸發信號的轉換,而且具有良好的抗干擾能力。此外,其并行處理結構可以保證三相橋臂開關同時動作,有效地提升了控制系統的整體性能。由于SVPWM信號發生器是用VHDL硬件描述語言實現的IP核.因而可簡便地應用于逆變器控制系統中。

評論