雙Nios II軟核在嵌入式系統(tǒng)中的應(yīng)用

引 言

本文引用地址:http://www.104case.com/article/82696.htmSOPC(System On Programmable Chip)即可編程片上系統(tǒng),或者說(shuō)是基于大規(guī)模FPGA的單片系統(tǒng),是美國(guó)Altera公司于2000年提出的。它將處理器、存儲(chǔ)器、I/O口、LVDS、CDR等系統(tǒng)設(shè)計(jì)需要的功能模塊集成到一個(gè)PLD器件上,將其構(gòu)建成一個(gè)可編程的片上系統(tǒng);具有靈活的設(shè)計(jì)方式,可裁減、可擴(kuò)充、可升級(jí),并具備軟硬件在系統(tǒng)可編程的功能。由于SOPC系統(tǒng)具有靈活的設(shè)計(jì)方式、高效的開(kāi)發(fā)手段、廉價(jià)的設(shè)計(jì)成本,可以實(shí)現(xiàn)過(guò)去不可能實(shí)現(xiàn)的更高的系統(tǒng)性能,因此它在通信和工業(yè)控制等領(lǐng)域正得到日益廣泛的應(yīng)用。

NiosII嵌入式處理器是FPGA生產(chǎn)廠商Altera公司推出的軟核CPU,是一種面向用戶(hù)的,可以靈活定制的通用精簡(jiǎn)指令集架構(gòu)(RISC)32位嵌入式CPU。NiosII以軟核的方式提供給用戶(hù),并專(zhuān)門(mén)在Altera公司的FPGA上實(shí)現(xiàn)了優(yōu)化,用于SOPC集成,最后在FPGA上實(shí)現(xiàn)。

本文將以VOD視頻點(diǎn)播系統(tǒng)為例,介紹采用NiosII構(gòu)建可編程片上系統(tǒng)SOPC的過(guò)程,以及雙CPU及其同步通信技術(shù)實(shí)現(xiàn)的視頻點(diǎn)播系統(tǒng)主機(jī)部分的設(shè)計(jì)思想和工作原理。

1 工程應(yīng)用

1.1 VOD相關(guān)內(nèi)容及雙CPU使用的必要性

視頻點(diǎn)播是一種交互式多媒體信息點(diǎn)播系統(tǒng)。其本質(zhì)是,信息使用者可根據(jù)自己的需求主動(dòng)獲取多媒體信息,打破目前用戶(hù)收看節(jié)目的被動(dòng)方式,使用戶(hù)從“播什么節(jié)目看什么節(jié)目”變成“想看什么節(jié)目就播什么節(jié)目”,從而按照自己的意愿通過(guò)網(wǎng)絡(luò)點(diǎn)播視頻服務(wù)器中的視頻節(jié)目。視頻點(diǎn)播以電視技術(shù)、計(jì)算機(jī)技術(shù)、通信技術(shù)為基礎(chǔ),它區(qū)別于信息發(fā)布的最大不同是用戶(hù)具有主動(dòng)性與選擇性。

VOD系統(tǒng)主要由3部分構(gòu)成:視頻點(diǎn)播服務(wù)器、傳輸網(wǎng)絡(luò)和視頻點(diǎn)播終端。當(dāng)點(diǎn)播終端發(fā)出點(diǎn)播請(qǐng)求時(shí),點(diǎn)播服務(wù)器就會(huì)根據(jù)點(diǎn)播信息,將存放在節(jié)目庫(kù)中的影視信息檢索出來(lái),并將視頻數(shù)據(jù)流通過(guò)高速傳輸網(wǎng)絡(luò)傳送到各個(gè)點(diǎn)播終端。點(diǎn)播終端接收到數(shù)據(jù)流后,將其解碼送到顯示器播放。

本設(shè)計(jì)采用一塊大容量硬盤(pán)作為VOD系統(tǒng)的點(diǎn)播數(shù)據(jù)源,將MPEG-1格式的影音文件按照FAT 32標(biāo)準(zhǔn)存放在硬盤(pán)上。由于視頻點(diǎn)播系統(tǒng)對(duì)硬盤(pán)訪問(wèn)的速度要求非常高,采用操作系統(tǒng)已無(wú)法滿(mǎn)足要求,所以利用SOPC技術(shù)將Altera公司的第2代嵌入式處理器NioslI嵌入到FPGA中,并通過(guò)DMA控制器直接對(duì)硬盤(pán)進(jìn)行最底層的操作,完成對(duì)影音文件的管理、檢索和數(shù)據(jù)讀取,充分發(fā)揮了FPGA的高速優(yōu)勢(shì)。本視頻點(diǎn)播服務(wù)器可以驅(qū)動(dòng)多達(dá)64個(gè)完全獨(dú)立的視頻終端。

為實(shí)現(xiàn)64路終端實(shí)時(shí)播放影片,必須對(duì)視頻數(shù)據(jù)流的傳輸速率嚴(yán)格規(guī)定,由于所有終端播放的文件均為MPEG-1格式,此格式下影片連續(xù)播放所需的數(shù)據(jù)流速率為1.416 Mb/s。本系統(tǒng)采用的數(shù)據(jù)收發(fā)器AM7968/7969的傳輸率為80 Mb/s,因此只要邏輯電路設(shè)計(jì)得當(dāng)且處理器定時(shí)發(fā)送數(shù)據(jù),就可達(dá)到視頻不間斷播放的設(shè)計(jì)要求。但點(diǎn)播系統(tǒng)在滿(mǎn)足視頻數(shù)據(jù)定時(shí)發(fā)送的條件下還應(yīng)當(dāng)實(shí)現(xiàn)讀取硬盤(pán)中存放MPEG-1數(shù)據(jù)的功能,對(duì)終端作出的點(diǎn)播信息作出及時(shí)響應(yīng)的功能,對(duì)USB中影音文件錄入的功能以及顯示屏的刷新與按鍵的處理功能。如果只采用一個(gè)處理器,則無(wú)法對(duì)每個(gè)環(huán)節(jié)作出及時(shí)響應(yīng),無(wú)法保證數(shù)據(jù)的定時(shí)發(fā)送和硬盤(pán)數(shù)據(jù)的按時(shí)讀取,所以采取在Altera公司的高性能FPGA中嵌入雙NiosII軟核的方式達(dá)到系統(tǒng)設(shè)計(jì)目的。

1.2 系統(tǒng)原理框圖及架構(gòu)

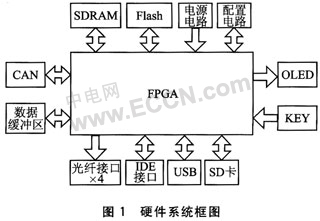

點(diǎn)播服務(wù)器主要由主控制器部分和外圍接口電路兩大部分組成,硬件系統(tǒng)框圖如圖1所示。主控制器單元主要由FPGA、存儲(chǔ)器電路、電源電路、時(shí)鐘、復(fù)位電路和配置芯片電路組成。外圍接口主要有:OLED顯示屏、動(dòng)態(tài)掃描鍵盤(pán)、數(shù)據(jù)緩沖區(qū)、SD卡、USB控制器、IDE接口、CAN總線接口、光纖接口等。

其中數(shù)據(jù)緩沖區(qū)由2個(gè)容量各為32 MB的SDRAM組成,用于暫時(shí)存放DMA控制器從硬盤(pán)讀出的視頻數(shù)據(jù);USB接口用于節(jié)目源的錄入;IDE接口用于與磁盤(pán)陣列連接;各終端的點(diǎn)播信息通過(guò)CAN總線送到點(diǎn)播服務(wù)器;視頻數(shù)據(jù)流通過(guò)4根光纖傳送到各個(gè)終端,每16個(gè)終端共用1根光纖,4根光纖可以驅(qū)動(dòng)64個(gè)終端。

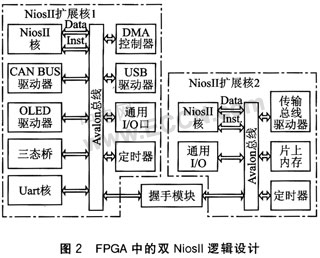

其中FPGA中,雙NiosII邏輯設(shè)計(jì)架構(gòu)實(shí)現(xiàn)如圖2所示。

NiosII Exectltion Core 1為主CPU,在這個(gè)處理器系統(tǒng)里面,DMA控制器負(fù)責(zé)將視頻數(shù)據(jù)從硬盤(pán)讀到緩沖區(qū)中;USB驅(qū)動(dòng)器負(fù)責(zé)從其他移動(dòng)存儲(chǔ)設(shè)備中錄入節(jié)目源到硬盤(pán)陣列;CAN BUS驅(qū)動(dòng)器負(fù)責(zé)接收終端的點(diǎn)播信息;Tristate Bridge用來(lái)連接外部程序存儲(chǔ)器SDRAM和Flash;OLED驅(qū)動(dòng)器用來(lái)控制OLED顯示屏;Uart核為RS232接口。

Nios II Execution Core 2為從CPU,專(zhuān)門(mén)用于向終端傳輸視頻數(shù)據(jù)流。最為關(guān)鍵的部分為T(mén)ransmit BUSDriver,它負(fù)責(zé)將DMA控制器寫(xiě)入緩沖區(qū)的數(shù)據(jù)讀出來(lái),并送給光纖發(fā)送模塊向終端發(fā)送。

此外,還必須有一個(gè)握手模塊(handshake module),負(fù)責(zé)2個(gè)CPU之間的信息傳遞,使2個(gè)CPU協(xié)調(diào)工作。

1.3 相關(guān)設(shè)置及添加過(guò)程

(1)NiosII CPU定制

根據(jù)不同設(shè)計(jì)的要求,有3種不同的內(nèi)核類(lèi)型可供選擇——快速型、經(jīng)濟(jì)型和標(biāo)準(zhǔn)型。快速型內(nèi)核具有最高的處理性能,經(jīng)濟(jì)型內(nèi)核具有最低的資源占用,而標(biāo)準(zhǔn)型在性能和資源之間作了個(gè)平衡。本設(shè)計(jì)中,CPU1需要實(shí)現(xiàn)硬盤(pán)數(shù)據(jù)讀取、顯示屏控制、總線請(qǐng)求、鍵盤(pán)處理等各種功能,因此選用標(biāo)準(zhǔn)型內(nèi)核;而CPU2只要定時(shí)讀取數(shù)據(jù)并發(fā)送至輸出模塊,功能單一,因此選取快速型內(nèi)核便可勝任。

(2)NiosII外圍設(shè)備定制

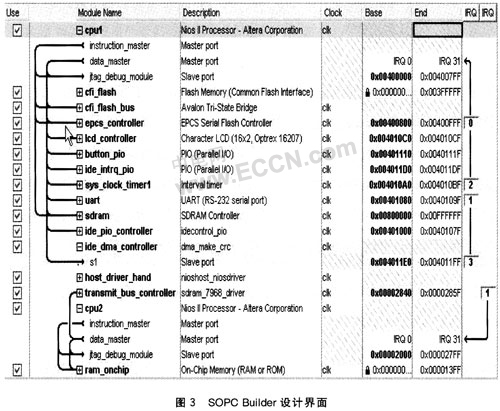

Altera公司推出SOPC設(shè)計(jì)技術(shù)的同時(shí)也為用戶(hù)提供了一些可以選用的存儲(chǔ)、接口和功能模塊的IP核。這些核可以直接添加到用戶(hù)的設(shè)計(jì)中。啟動(dòng)SOPC Builder后,在GUI界面中左邊是可供用戶(hù)選擇的模塊資源池,包括處理器和各種外設(shè)(其中有自己開(kāi)發(fā)的模塊),也包括第3方開(kāi)發(fā)的模塊。用戶(hù)模塊也可以放入資源池,用戶(hù)邏輯在第一次定義后,就可以將其放人模塊資源池,以后使用時(shí)當(dāng)成普通模塊一樣使用。

(3)自定義控制組件設(shè)計(jì)

Altera公司提供了使用第3方核的簡(jiǎn)單接口。只要符合這些接口規(guī)范,就可以使用各種IP核進(jìn)行SOPC設(shè)計(jì)。

由于Altera公司并未直接提供硬盤(pán)、CAN控制器、USB及2個(gè)CPU握手模塊等接口,因此必須自己設(shè)計(jì)接口連接各種器件和處理器。這些接口既要符合Avalon總線規(guī)范,又要滿(mǎn)足各種器件的工作時(shí)序。圖3為點(diǎn)播服務(wù)器系統(tǒng)在SOPC Builder工作窗口中的截取圖。

評(píng)論