“RISC +類FPGA”架構共同提供優異的再配置性

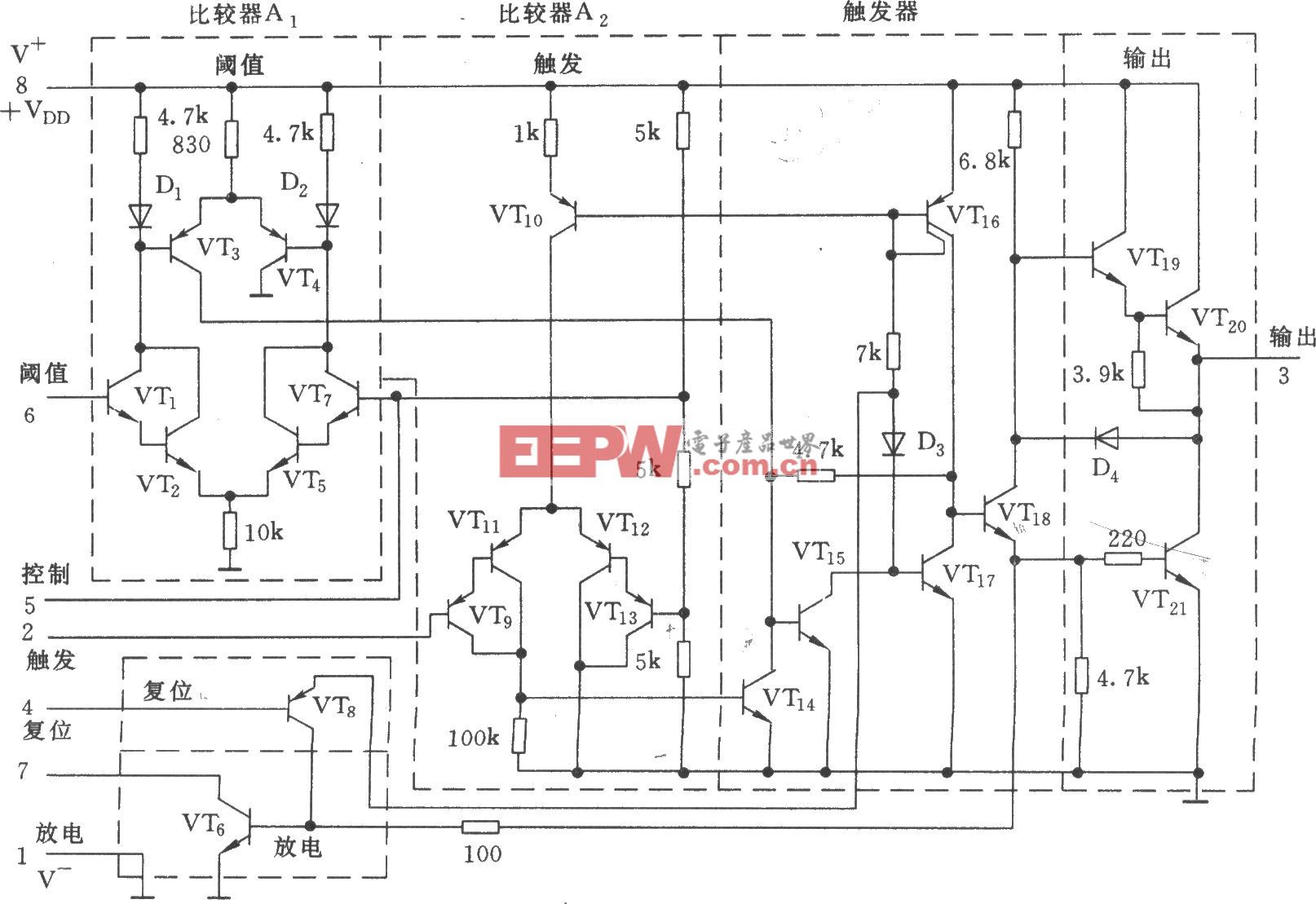

它與其它 CPU+FPGA 組合的不同之處在于,它把可編程邏輯電路組織為一個可編程硬件塊,位于處理器的數據路徑內部。其結果就是一種具有新指令的RISC 機器——這些指令滿足了應用的處理需求,但又沒有訪問常規協處理器結構所需的系統開銷。

你可以在用 C/C++ 寫的單一工具流程中,通過為應用編寫代碼,或配置各硬件元件的方式,來對該裝置編程。Banta 聲稱,該架構非常靈活,以便處理多種計算密集型應用,同時功能足夠強大,從而具有很高的成本效率;單個裝置就可以完成以前可能需要多個處理器才能完成的各種任務。

可編程部分被稱為 ISEF(指令集擴展結構)。由于它比標準 FPGA 的通用性低很多,因此單位面積邏輯功能的密度更大。不過,Stretch 公司目前既沒有披露密度,也沒有披露可編程邏輯電路的數量。它也沒有公布內核對 FPGA 的面積之比。

代碼是以 C/C++ 編寫的應用程序開始的,經過一個相當常規的剖析運作來識別各個計算密集型回路。在識別了這些部分之后,編譯器把嵌在它們內部的代碼轉換為針對 ISEF 邏輯的配置代碼,這樣,就程序的其它部分而言,代碼已被壓縮成單個指令。

SS架構的創意在于在Xtensa可配置處理器的數據路徑內部加入一個類FPGA的ISEF,完成針對不同應用的可配置性設計。

它通過三條通往寄存器堆的 128 比特寬的路徑來處理 ISEF,該寄存器堆緊密集成至內核,并可被配置來提供很寬的并行數據路徑。因此,所有數據很接近執行單元,它在定時和功率方面的效率都很高。該公司把壓縮關鍵代碼和創建一項配置的過程描述為自動進行的,不過你并不參與對配置做優化的過程。如何知道自己擁有了最優的解決方案?Banta 表示,當你實現了對 ISEF 的一次設置,它只“接觸”數據一次——取得數據,對數據做運算,返回結果——這時,你就知道自己已經完成了這個過程。

你可以在引導時利用你需要的所有運算符一次性配置 ISEF,從而使它具有多個運算符的寬度和深度。或者,你可以用所需的運算符快速地加載它。你可以執行這些任務,或利用某種高速緩存型機制。Banta 聲稱,該裝置的總效率非常高,這樣在多數情況下,偶然的“高速緩存缺失”(導致運算符被加載)將不再是問題。據稱,編譯幾分鐘就可以“填滿” ISEF。Stretch 公司聲稱,加載一項新的 ISEF 配置只需大約 100 微秒。

Stretch 公司已經出示了關于 Telemark 套件的 EE-MBC(EDN 嵌入式微處理器基準聯盟)結果,它們表明,優化過程(對硬件編碼)使性能提高200 多倍。Banta 表示,更重要的是,對于相同的應用代碼而言,運行于 300MHz 的這種處理器在性能上超過了運行頻率高達 720MHz 的“純”DSP。200 多倍的性能改善是針對 EEMBC 代碼的,不過任何計算密集型代碼集都應該會達到類似的性能改善。

Banta 列舉了人們也許能夠應用其概念的三種情況:當人們必須使用多個處理器時;當人們必須使用標準處理器,并通過高性能的耦合 FPGA 來卸載對關鍵功能的處理時;或當人們必須構建復雜的 ASIC 時。

各種 S5 部件在 I/O 能力方面有所不同,這取決于市場和價格范圍,從針對典型消費應用的 35 美元(25,000 件)到針對電信、聯網、軍事以及安全應用的大約 100 美元(10,000 件)。功率將為 1 至 3W,因此 Banta 并不推薦這種處理器用于“袖珍產品”。他指出,公司要“把精力集中于速度和性能”。

評論