智能型動態圖像追蹤自控車

2. 2個 CMOS 傳感器擷取:

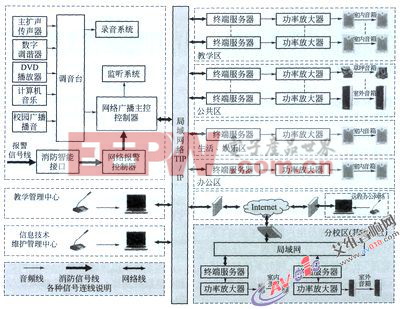

本文引用地址:http://www.104case.com/article/82032.htm撰寫鏡頭圖像擷取的控制硬件電路,并利用DE2發展板上的雙IDE接口(Expansion Header1,2)可同時擷取到雙重鏡頭的圖像。

3. 多端口SDRAM 控制器:

利用Mega Wizard Plug-In Manager來生成三寫三讀的六接口FIFO(以內置RAM實現),讓二組CMOS 傳感器擷取及一組VGA 控制器能讀寫SDRAM設備。

4. VGA 控制器 和圖像處理:

撰寫VGA輸出的硬件控制電路,并在圖像輸出的同時,進行X軸及Y軸的圖像數據統計,并將結果存于片上內存(On-Chip Memory)之中,以便Nios處理器來讀取。

. SOPC系統端接口設定

圖4 系統端SOPC接口設定

由DE2發展板所提供的范例新增用戶自定腳位來控制自制的外圍電路,并通過PLL生成100MHz頻率的時鐘源供SDRAM來使用,如圖5所示。

圖5 cpu_0在SOPC(上)及在NIOS IDE(下)中的內存配置

. 系統軟件執行時內存的配置

由于開發板上的SDRAM已被CMOS 傳感器擷取及VGA 控制器所使用,所以cpu_0及cpu_1的程序內存是放于Flash上,而cpu_0執行程序時的例外向量是放于SRAM上;而cpu_1是放于片上內存之中,當然在NIOS IDE開發該CPU的軟件時,也必須分別要把變量堆疊區指定到相關的內存之中,如圖5、圖6所示。

圖6 cpu_1在SOPC(上)及在NIOS IDE(下)中的內存配置

效能參數

評論