雙內核處理器勝任未來網絡計算

——

雙內核處理器勝任未來網絡計算

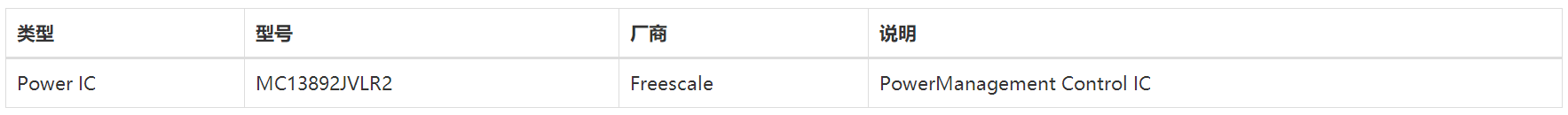

市場對于未來網絡處理器的要求已經越來越清晰:在可接受的成本與功耗基礎上實現更高的計算性能。飛思卡爾公司(Freescale)對此的解決方案是:開發一種內含雙處理器內核的網絡處理器MPDC8641D。該器件中采用90納米SOI工藝制造,集成了兩個基于32位PowerPC處理器架構的e600內核,單一e600內核的性能可達到1.5GHz,飛思卡爾預計這種雙核結構將使最終的網絡處理器性能加倍。

雙核結構與傳統的單核結構相比,優勢是顯而易見的。首先,雙內核處理器從芯片硅成本來講雖然比單核處理器高,但由于其可取代兩顆獨立單核處理器和一顆系統控制器芯片,因此可簡化PCB電路的設計,有效節省應用系統的成本。其次,與通過兩個單內核處理器協同工作完成的性能提升解決方案相比,單芯片內部的雙內核之間可以通過高速內部總線實現更大的帶寬通信,從而避免了芯片外部互連的低速PCI總線成為性能瓶頸。MPDC8641D中采用了MPX總線,其最高帶寬達667MHz,可使內核間的通信延遲降到最低限度。第三,由于集成了雙內存控制器,MPDC8641D中存儲器帶寬得到了擴展,并降低了延遲。此外,雙內核架構還可使兩個內核保持高度的緩存一致性,因為某一內核可將其緩存中的最新數據直接快速拷貝到另一內核中,而無需通過存儲器。根據Freecale提供的數據,MPDC8641D的功率在15W~25W之間。

與這種突出的計算性能相匹配,MPDC8641D選擇了RapidIO串行線路接口作為外部系統互連接口,以實現其與周邊設備之間的高速互連。同時,MPC8641D處理器還內嵌了四個以太網MAC控制器,支持10/100Mbps及千兆以太網,可對通過以太網(包括IPv4、IPv6、TCP、UDP以及VLAN)傳播的協議的識別和檢索進行加速。此外,它還支持原有的外圍與主機設備之間通過PCI Express接口的連接。

這種雙核結構實際上還可以帶來設計開發上的靈活性。比如,在低帶寬應用中,系統開發商可以利用MPC8641D的某一個內核來管理數據面處理,而用另一個內核管理控制面;或者用一個內核管理數據面的信號發射,而另一個內核管理信號接收;在高帶寬應用中,兩個內核都可與一顆網絡處理器或ASIC配合工作,其中一個內核卸載任務,如分類、安全和高質量。開發商還可選擇讓雙內核使用同一操作系統,從而簡化到現有系統升級到采用雙內核系統的軟件移植。目前已經有Enea Embedded Technology、Green Hills Software、Metrowerks、QNX、Wind River等開發商表示會為這款網絡處理器提供軟件或開發工具支持。

雙核結構與傳統的單核結構相比,優勢是顯而易見的。首先,雙內核處理器從芯片硅成本來講雖然比單核處理器高,但由于其可取代兩顆獨立單核處理器和一顆系統控制器芯片,因此可簡化PCB電路的設計,有效節省應用系統的成本。其次,與通過兩個單內核處理器協同工作完成的性能提升解決方案相比,單芯片內部的雙內核之間可以通過高速內部總線實現更大的帶寬通信,從而避免了芯片外部互連的低速PCI總線成為性能瓶頸。MPDC8641D中采用了MPX總線,其最高帶寬達667MHz,可使內核間的通信延遲降到最低限度。第三,由于集成了雙內存控制器,MPDC8641D中存儲器帶寬得到了擴展,并降低了延遲。此外,雙內核架構還可使兩個內核保持高度的緩存一致性,因為某一內核可將其緩存中的最新數據直接快速拷貝到另一內核中,而無需通過存儲器。根據Freecale提供的數據,MPDC8641D的功率在15W~25W之間。

與這種突出的計算性能相匹配,MPDC8641D選擇了RapidIO串行線路接口作為外部系統互連接口,以實現其與周邊設備之間的高速互連。同時,MPC8641D處理器還內嵌了四個以太網MAC控制器,支持10/100Mbps及千兆以太網,可對通過以太網(包括IPv4、IPv6、TCP、UDP以及VLAN)傳播的協議的識別和檢索進行加速。此外,它還支持原有的外圍與主機設備之間通過PCI Express接口的連接。

這種雙核結構實際上還可以帶來設計開發上的靈活性。比如,在低帶寬應用中,系統開發商可以利用MPC8641D的某一個內核來管理數據面處理,而用另一個內核管理控制面;或者用一個內核管理數據面的信號發射,而另一個內核管理信號接收;在高帶寬應用中,兩個內核都可與一顆網絡處理器或ASIC配合工作,其中一個內核卸載任務,如分類、安全和高質量。開發商還可選擇讓雙內核使用同一操作系統,從而簡化到現有系統升級到采用雙內核系統的軟件移植。目前已經有Enea Embedded Technology、Green Hills Software、Metrowerks、QNX、Wind River等開發商表示會為這款網絡處理器提供軟件或開發工具支持。

評論