基于FPGA的并行DSP芯片實(shí)時(shí)圖像編碼平臺(tái)

引言

本文引用地址:http://www.104case.com/article/81619.htm圖像壓縮技術(shù)在現(xiàn)代生活中的地位越來(lái)越重要,隨著現(xiàn)在的DSP處理數(shù)據(jù)速度的提高,對(duì)傳統(tǒng)的圖像壓縮而言,單片DSP即可達(dá)到很好的效果。但由于信息量的增長(zhǎng),尤其是高清晰度等概念的提出,系統(tǒng)的處理數(shù)據(jù)能力也需要提高,尤其是要求實(shí)時(shí)圖像壓縮編碼時(shí),單片DSP無(wú)法勝任這樣的工作,即使是專(zhuān)用芯片也無(wú)法達(dá)到相應(yīng)的要求。近十年來(lái)DSP技術(shù)飛速發(fā)展,在DSP主頻得到重大突破的同時(shí),其并行技術(shù)和外部通信技術(shù)也得到了很大的提高。現(xiàn)在各大DSP廠商所生產(chǎn)的DSP都在數(shù)據(jù)級(jí)和指令級(jí)上實(shí)現(xiàn)了不同的并行技術(shù),如TI公司的TMS320 C64XX系列和ADI公司的Tiger SHARC系列芯片。本文主要介紹的是采用ADI公司的ADSP-TS201S芯片實(shí)現(xiàn)的多DSP系統(tǒng)。

ADSP-TS201S的并行技術(shù)

ADSP-TS201S芯片是ADI公司在2004年推出的一款芯片,具有600MHz的時(shí)鐘頻率,1.67ns的指令周期。ADSP-TS201S芯片通過(guò)外部口(External Port)和鏈路口(Link Ports)兩種接口技術(shù)對(duì)多處理器提供了有力的支持,這種多處理能力有以下特性:

·同一條通用總線支持多達(dá)8片DSP同時(shí)工作;

·提供多處理器的分布式總線仲裁邏輯,實(shí)現(xiàn)多處理器的無(wú)縫連接;

·用Link port 實(shí)現(xiàn)多處理器間的高速點(diǎn)對(duì)點(diǎn)通信。

External Port提供了一個(gè)統(tǒng)一的地址空間,這個(gè)地址空間可以讓每個(gè)處理器直接訪問(wèn)ADSP-TS201S芯片內(nèi)部的內(nèi)存和寄存器。該DSP的分布式總線仲裁邏輯可實(shí)現(xiàn)多處理器的無(wú)縫連接,并且支持多達(dá)八片ADSP-TS201S芯片和一片主處理器同時(shí)工作。仲裁邏輯還可以防止一個(gè)處理器占用外部總線時(shí)間過(guò)長(zhǎng)。

ADSP-TS201S芯片的四個(gè)Link Ports端口是多處理器方案的另一條實(shí)現(xiàn)路徑,Link Ports支持處理器間高達(dá)4GB每秒的數(shù)據(jù)傳輸速率,每條總線也提供1GB每秒的速率,也就是說(shuō)四條總線總共提供4.87GB每秒的處理器間通信帶寬。

共享存儲(chǔ)并行DSP系統(tǒng)

根據(jù)結(jié)構(gòu)的不同,多處理器并行系統(tǒng)可以分為分布式并行DSP系統(tǒng)和共享存儲(chǔ)器式并行DSP系統(tǒng),ADSP-TS201S 均支持這兩種并行處理器結(jié)構(gòu)。常見(jiàn)的共享存儲(chǔ)并行DSP系統(tǒng)結(jié)構(gòu)如圖1所示。

共享存儲(chǔ)并行DSP系統(tǒng)的優(yōu)勢(shì):由于它采用共享存儲(chǔ)結(jié)構(gòu),所以比較節(jié)省存儲(chǔ)資源。其次,共享總線節(jié)省了總線資源,可以提高系統(tǒng)的資源使用率。最后,也是最主要的,它采用主從式協(xié)同工作,使得各處理器分工明確,便于實(shí)現(xiàn)和調(diào)試。

然而考慮到圖像編解碼時(shí),完全共享存儲(chǔ)和總線往往會(huì)引起系統(tǒng)資源緊缺,而且在要求大量數(shù)據(jù)實(shí)時(shí)處理(如對(duì)高清圖像、視頻編解碼)時(shí),完全共享存儲(chǔ)不能勝任。同時(shí),采用DSP作為主控制器,不便于以后的系統(tǒng)升級(jí)和維護(hù)。最后,單一的共享存儲(chǔ)式結(jié)構(gòu)在DSP之間的通信方面明顯不如分布式。下文介紹的基于FPGA的改進(jìn)共享存儲(chǔ)并行DSP系統(tǒng),更好的發(fā)揮了共享存儲(chǔ)并行DSP系統(tǒng)的優(yōu)勢(shì),同時(shí)改進(jìn)了上述缺點(diǎn)。

實(shí)時(shí)圖像編碼系統(tǒng)實(shí)現(xiàn)

本系統(tǒng)采用改進(jìn)的共享存儲(chǔ)結(jié)構(gòu)設(shè)計(jì),對(duì)一般的共享存儲(chǔ)并行DSP系統(tǒng)而言具有以下特點(diǎn):

·SP之間采用分布耦合式,更加便于DSP之間的數(shù)據(jù)交換;

·引入DSP簇的概念,采用DSP簇共享存儲(chǔ),解決存儲(chǔ)資源瓶頸;

·FPGA做主控制器,利于硬件實(shí)現(xiàn)并易于維護(hù);

·擴(kuò)展性較強(qiáng),可以級(jí)聯(lián)以適應(yīng)更高要求;

·采用獨(dú)立電源供電,減少電源線路對(duì)系統(tǒng)線路影響

本系統(tǒng)由兩部分組成,第一部分為處理部分(Processboard),第二部分為控制預(yù)處理部分(Mainboard)。

處理部分結(jié)構(gòu)

Processboard由四片ADSP-TS201S組成,DSP之間采用松緊耦合的方式,構(gòu)成一個(gè)靈活高效的多處理單元并行結(jié)構(gòu)。所謂的松耦合是指四片DSP采用Link ports實(shí)現(xiàn)雙向互聯(lián)的方式。緊耦合是指兩片DSP構(gòu)成一個(gè)簇,DSP的外部總線連在簇總線上,外部存儲(chǔ)器也接在簇總線上。外部存儲(chǔ)器和各DSP的片內(nèi)存儲(chǔ)器作為共享資源都可以被總線上的DSP訪問(wèn)。這種方式充分利用AD I公司DSP片上無(wú)縫連接的優(yōu)勢(shì)。Processboard結(jié)構(gòu)圖如圖2所示。

本系統(tǒng)四片DSP拿出三組Link ports資源構(gòu)成雙向十字環(huán)連接,另外每片DSP還有一組Link ports與Mainboard連接,用于系統(tǒng)連部分之間的數(shù)據(jù)通信。這種主芯片近似完全對(duì)稱(chēng)的結(jié)構(gòu)有利于PCB的合理布線。所有DSP的數(shù)據(jù)、地址以及控制信號(hào)等均通過(guò)一個(gè)150針的接口與Mainboard相連,構(gòu)成一個(gè)完整的系統(tǒng)平臺(tái)。

在這樣的系統(tǒng)結(jié)構(gòu)中,待處理的信號(hào)可以經(jīng)過(guò)Link ports送至Mainboard上的FPGA,或者通過(guò)速度更快的LVDS接口經(jīng)串并轉(zhuǎn)換芯片輸入。由于兩個(gè)簇總線均接至FPGA,故輸入數(shù)據(jù)可以通過(guò)FPGA內(nèi)部做成數(shù)據(jù)總線開(kāi)關(guān),使得兩個(gè)DSP簇可以“乒乓”讀取和處理連續(xù)不斷輸入的待處理信號(hào)。處理完成的數(shù)據(jù)經(jīng)Link ports送回至Mainboard。對(duì)于一個(gè)DSP簇,利用緊耦合的方式,用一片8M×32位的SDRAM存放數(shù)據(jù)塊,通過(guò)DMA技術(shù)可在DSP內(nèi)核進(jìn)行信號(hào)處理時(shí)高速傳輸數(shù)據(jù),提高了實(shí)時(shí)性并最大限度緩解了總線瓶頸。簇內(nèi)的DSP及外圍設(shè)備接口通過(guò)32位地址總線互聯(lián),映射到統(tǒng)一存儲(chǔ)空間。因此對(duì)外部存儲(chǔ)空間的訪問(wèn)就等同于訪問(wèn)外部接口設(shè)備。外部總線工作在100 MHz,單片DSP的總線吞吐率達(dá)到1 GB 每秒。

控制預(yù)處理部分結(jié)構(gòu)

Mainboard由兩個(gè)FPGA和一片ADSP-TS201S組成。系統(tǒng)采用模塊化設(shè)計(jì),可分為三個(gè)模塊。控制模塊由兩個(gè)FPGA完成系統(tǒng)的控制功能。后處理模塊包括DSP及其外圍電路。擴(kuò)展模塊由八個(gè)150針的接口組成,完成與Processboard的通信。為擴(kuò)展存儲(chǔ)空間,該系統(tǒng)上包含了四片SRAM和四片16位SDRAM(均分為兩組,擴(kuò)展為32位),兩個(gè)FPGA還可以用來(lái)做一部分預(yù)處理(如JPEG2000圖像壓縮編碼中的小波預(yù)處理)。Mainboard結(jié)構(gòu)如圖3所示。

系統(tǒng)供電方案

由于本系統(tǒng)的元器件較多且大部分工作功率較大,在每塊板上各自設(shè)計(jì)供電系統(tǒng)是不合適的。同時(shí)由于系統(tǒng)內(nèi)數(shù)據(jù)交換速度達(dá)到數(shù)百兆每秒,將電源集成至系統(tǒng)內(nèi)部電路板會(huì)影響系統(tǒng)正常工作甚至導(dǎo)致各種布線問(wèn)題。

本系統(tǒng)采用了獨(dú)立電源供電,即整個(gè)系統(tǒng)供電都來(lái)自一個(gè)獨(dú)立設(shè)計(jì)的電源系統(tǒng)。這種供電方式類(lèi)似于個(gè)人PC上的供電系統(tǒng)。電源系統(tǒng)結(jié)構(gòu)如圖4所示。

電源系統(tǒng)芯片采用TI公司的電源模塊PTH系列,該系列芯片具有穩(wěn)定易使用且供電功率高的特點(diǎn)。5V輸入電壓系統(tǒng)后經(jīng)過(guò)五片PTH芯片轉(zhuǎn)換成所需的電壓(1.0V,1.5V,1.8V,2.5V,3.3V),經(jīng)電源接口送入Mainboard和Processboard。

系統(tǒng)工作流程

當(dāng)高速圖像數(shù)據(jù)傳入Mainboard上的大FPGA時(shí),該FPGA實(shí)現(xiàn)對(duì)數(shù)據(jù)的分組和預(yù)處理,如果數(shù)據(jù)量超過(guò)FPGA內(nèi)部存儲(chǔ)器的范圍,則將數(shù)據(jù)放入外部存儲(chǔ)器中進(jìn)行緩存;數(shù)據(jù)分組完畢后由大FPGA負(fù)責(zé)將數(shù)據(jù)傳輸至Processboard,Processboard并行處理完后再分別傳送回Mainboard的小FPGA(如果數(shù)據(jù)分組適當(dāng),數(shù)據(jù)將同步傳送至小FPGA),最后由小FPGA實(shí)現(xiàn)數(shù)據(jù)重組和合并功能后,送至Mainboard的DSP進(jìn)行后期處理,處理完再由輸出端口輸出。這樣系統(tǒng)完成了一次處理過(guò)程。

系統(tǒng)工作時(shí)最大的問(wèn)題是并行任務(wù)分配與調(diào)度問(wèn)題。任務(wù)分配和算法的好壞直接影響到并行系統(tǒng)的性能,影響系統(tǒng)執(zhí)行任務(wù)的效率,進(jìn)而影響系統(tǒng)的實(shí)時(shí)性。在多DSP 系統(tǒng)中,任務(wù)分配使得各個(gè)處理器能夠均勻分配到子任務(wù),使各處理單元的空閑時(shí)間減少,從而得到較高的執(zhí)行效率。例如在圖像編碼中把一幅圖像平均分割,使各處理器得到相同大小的子圖像,有效提高了系統(tǒng)編碼效率,滿(mǎn)足其實(shí)時(shí)性要求。由于本系統(tǒng)的復(fù)雜度,采用FPGA來(lái)做任務(wù)分配與調(diào)度是可行的。

實(shí)時(shí)圖像編碼系統(tǒng)的擴(kuò)展

由于在設(shè)計(jì)上采用控制與處理的分離設(shè)計(jì),這個(gè)系統(tǒng)有非常好的擴(kuò)展性。如圖5所示,系統(tǒng)對(duì)Processboard和Mainboard的擴(kuò)展都支持,具體表現(xiàn)在以下幾方面:

(1)Processboard的擴(kuò)展—Mainboard給出了四組有效的Processboard擴(kuò)展接口,也就是說(shuō)最多可以擴(kuò)展至四塊Processboard。圖中畫(huà)出了八個(gè)接口,其中兩兩一組,目的是方便調(diào)試兩板之間的通信,還利于整個(gè)系統(tǒng)的散熱。

(2)Mainboard的板級(jí)擴(kuò)展—通過(guò)板上預(yù)留的接口,Mainboard可實(shí)現(xiàn)32位的級(jí)聯(lián)擴(kuò)展。當(dāng)接上其余Mainboard時(shí),系統(tǒng)工作方式如下:級(jí)聯(lián)后,每一級(jí)專(zhuān)門(mén)負(fù)責(zé)自己的任務(wù),第一塊板的所有FPGA都用來(lái)實(shí)現(xiàn)預(yù)處理和基本控制,其余級(jí)聯(lián)板可以用來(lái)完成類(lèi)似于Processboard的任務(wù),也可以完成多級(jí)處理的任務(wù),這種工作方式適用于多級(jí)處理。

Processboard擴(kuò)展時(shí)會(huì)遇到時(shí)鐘資源匱乏的問(wèn)題,由于每片F(xiàn)PGA所提供的全局始終資源僅為16個(gè),而每擴(kuò)展一塊Processboard時(shí)所需的資源是5個(gè),所以采用單片F(xiàn)PGA時(shí)最多只能實(shí)現(xiàn)三塊Processboard的擴(kuò)展。為解決這個(gè)問(wèn)題,我們采用了雙FPGA的設(shè)計(jì)方法,兩塊FPGA分別掌管Processboard的進(jìn)出時(shí)鐘,這樣設(shè)計(jì)最大的不僅將時(shí)鐘資源翻倍,同時(shí)還可以方便FPGA的編程,便于系統(tǒng)調(diào)試。

系統(tǒng)性能

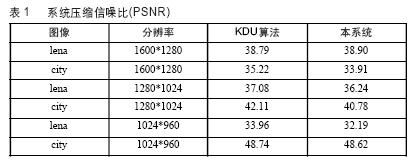

選取分辨率分別為1600×1280、1280×1024、1024×960的6副圖像,利用實(shí)時(shí)圖像編碼系統(tǒng)進(jìn)行圖像編碼,采用JPEG2000圖像壓縮編碼標(biāo)準(zhǔn),表1為該系統(tǒng)的壓縮結(jié)果和采用KDU算法的軟件壓縮結(jié)果,通過(guò)對(duì)比能發(fā)現(xiàn),該系統(tǒng)壓縮效果的PSNR值與KDU的相差甚小,而且可以達(dá)到在分辨率1440×1280的情況下實(shí)現(xiàn)每秒45幀的素壓縮速度,完全可以勝任圖像序列和高清視頻的實(shí)時(shí)壓縮要求。

結(jié)語(yǔ)

通過(guò)對(duì)共享存儲(chǔ)并行DSP系統(tǒng)的研究與改進(jìn),本文以高性能的 ADSP-TS201S芯片為基礎(chǔ),設(shè)計(jì)出一個(gè)改進(jìn)的基于FPGA的多處理器并行系統(tǒng)。通過(guò)實(shí)踐證明,該系統(tǒng)能夠?qū)崿F(xiàn)對(duì)高清圖像和視頻的實(shí)時(shí)壓縮編碼。

參考文獻(xiàn):

1. Analog Devices INC. ADSP-TS201 TigerSHARC Embedded Processor Data Sheet (Rev. A). 2004

2. Analog Devices INC. ADSP-TS201 TigerSHARC Processor Hardware Reference, Revision 1.0, November 2004

3. 劉書(shū)明,蘇 濤等. TigerSHARC DSP應(yīng)用系統(tǒng)設(shè)計(jì). 北京:電子工業(yè)出版社, 2004.

4. 王二力,李世杰.基于ADSP-TS101的多DSP并行處理系統(tǒng).單片基于嵌入式應(yīng)用,2005(12)

評(píng)論