基于FPGA的VXI總線寄存器基模塊接口電路設計(06-100)

開機初始化

本文引用地址:http://www.104case.com/article/81437.htm根據VXI總線時序,在電源接通后,背板總線上SYSRST信號由低變高,以使SOFTRST信號由高變低并啟動一次模塊復位自檢過程。根據VXI總線協議,模塊復位自檢應包括各寄存器(基本配置寄存器和用戶定義操作寄存器)的初始化和功能電路的初始化。

模塊和寄存器譯碼

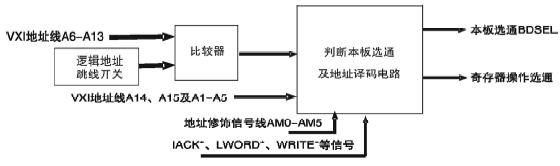

一個VXIbus系統中最多可有256個器件,每個器件都有一個唯一的邏輯地址,編號從0到255。通常規定00H邏輯地址賦予插入0號槽的為系統提供公共資源的資源管理器和0號槽器件,而FFH號在上電時賦予系統的所有DC器件,其它的01H--FEH號分配給任意的SC器件。每個器件的邏輯地址由人工通過“邏輯地址選擇器”設定。器件選通是由VXI的地址線A6-A13和地址修改線AM0-AM5來共同實現的,具體原理如圖2所示。邏輯地址作為該器件的標準組態/操作寄存器的基地址。每個VXIbus器件有一組64字節的標準組態/操作寄存器位于系統A16尋址空間的高16K字節。VXIbus系統中,各器件內部的各可尋址單元是統一分配的。每個器件都支持16位尋址方式,每個器件64字節的最小地址空間是在寄存器基地址的基礎上向上疊加的,如果器件的邏輯地址為V,則器件寄存器的基地址可由下式給出:

器件寄存器的基地址=215+214+V×64

選中模塊的條件用邏輯表達式描述為

CARDADDR=(A[13..6]=LA[7..0])&&(AM [5..0]=2DH||A M[5..0]=29H)&&(IACK* =1)&&(LWORD*=1),也可用語言描述為:當器件被尋址時,接收地址線A01-A15及地址修改線AM0-AM5上的信息,并將其與本模塊上硬件地址開關設置的邏輯地址相比較,如果AM0-AM5上的邏輯值為29H或2DH,地址線A15,A14均為1,并且A13-A6上的邏輯值與模塊的邏輯地址相等時,該器件被選通,接著其譯碼結果被送往下一級譯碼控制,通過對地址A01-A05進行譯碼選中模塊在16位地址空間的操作寄存器。

評論