數字化全雙工語音會議電路(06-100)

——

基于FPGA的全雙工語音會議電路

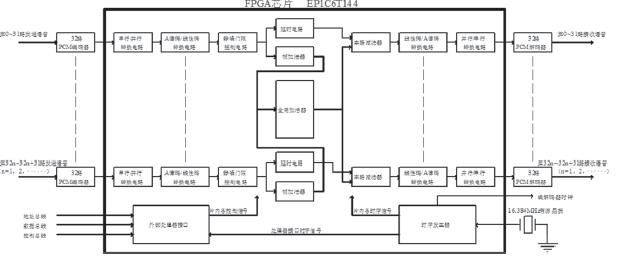

本文引用地址:http://www.104case.com/article/81181.htm 圖1即為基于FPGA的數字化全雙工語音會議電路的原理框圖。

圖1中間框內的電路全部由一片FPGA芯片來實現。模擬語音信號通過PCM編碼器成為串行數字語音信號送入FPGA芯片。PCM語音編碼以32個時隙組成1幀,每路語音占用1個時隙。為了發揮FPGA并行處理信號的長處,把輸入語音信號每32路作為1組,經編碼后成為1幀PCM信號,FPGA對各幀信號進行并行處理。例如輸入是128路語音時,FPGA就同時處理4幀PCM信號。經FPGA處理后的信號最終仍然分幀輸出,經PCM解碼器后還原為模擬語音。圖中為了說明信號流程把PCM編碼器和解碼器分開來畫,實際上編解碼器是集成于同一芯片內的。

以下簡要說明FPGA內各電路模塊的功能:

串行/并行轉換電路

輸入到FPGA的串行PCM信號通過該電路將每時隙8比特的串行數據轉換成8位的并行信號,然后暫存在用FPGA片內RAM資源設計成的雙端口存儲器中。雙端口存儲器的另一端按要求的時序依次輸出各并行數據,供后續處理。

A律碼/線性碼轉換電路

本部分電路完成8位A律PCM碼到13位線性碼的轉換,以便隨后對語音進行線性運算。轉換電路用AHDL語言編寫。在每幀的125μs時間內32路PCM語音信號分時使用本電路,因此每32路可共用1個碼型轉換電路。

評論