FPGA在語音存儲與回放系統中的應用

1 引言

本文引用地址:http://www.104case.com/article/80373.htm隨著數字信號處理器、超大規模集成電路的高速發展,語音記錄技術已從模擬錄音階段過渡到數字錄音階段。在數字化錄音技術中,壓縮后的語音數據有些存儲在硬盤中,有些存儲在帶有掉電保護功能的RAM或FLASH存儲器中。筆者介紹的語音存儲與回放系統,未使用專用的語音處理芯片,不需要擴展接口電路,只利用FPGA作為核心控制器,就能完成語音信號的數字化處理,即實現語音的存儲與回放。

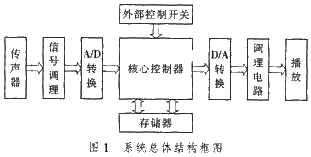

2 系統總體結構

數字化語音存儲與回放系統的基本工作原理是將模擬語音信號通過模數轉換器(A/D)轉換成數字信號,再通過控制器控制存儲在存儲器中;回放時,由FPGA控制將數據從存儲器中讀出,然后通過數模轉換器(D/A)轉換成模擬信號,經放大后由揚聲器輸出。本設計方案系統總體結構框圖如圖1所示。

3 各部分電路設計

3.1 音頻前置放大器

聲音通過傳聲器轉換成微弱的電信號(mV級),必須進行放大才能經A/D轉換送入單片機。可采用專用的音頻前置放大器。本系統采用頻帶寬、噪聲低、失真小的NE5534芯片,如圖2所示。

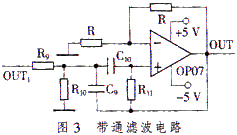

3.2 帶通濾波器(BPF)

本系統選用有源帶通濾波器,由運算放大器OP07組成。其中心頻率f0=1 kHz,通帶為300 Hz~3.4 kHz。如圖3所示。

3.3 A/D轉換器

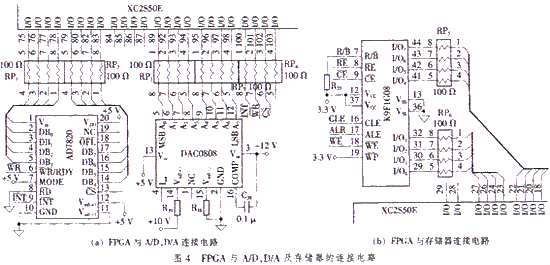

帶通濾波器的輸出信號經采樣保持(LF398)后送A/D轉換電路進行抽樣和量化,將模擬信號轉換成8 bit數字信號。本系統選用AD7820芯片。

AD7820有2種工作模式,由MODE決定:當MODE接高電平時芯片工作在WR模式下;當接低電平時工作在RD模式下。本系統將芯片設置在WR模式的S-A方式(最簡單的方式)下,即:MODE接高電平,RD和CS持續接低電平。當WR變低時開始轉換,在WR上升沿的700 ns后,轉換數據被輸出。

本系統采樣頻率fs=250 kHz,字長8 bit。 AD7820為高速、微型、單通道A/D轉換器,采用逐次比較技術,轉換時間1.36μs,轉換范圍0~5 V,使用單電源+5 V供電。逐次比較使用31個比較器,1個高4位ADC和1個低4位ADC,輸入信號被抽樣電路追蹤和保持;有專門ADC輸出接口設計,可與任何端口連接而不需要接口路基電路。所有的數字信號輸出使用鎖存與三態緩沖電路,使其可直接與微處理器的數據總線和系統的輸入端口相連接。

3.4 D/A轉換器

語音回放需將存儲的數字信號通過D/A轉換器轉換成語音模擬信號。本系統選用DAC0808,其為8 bitD/A集成電路芯片,滿量程輸出需要150 ns,用±5 V電壓供電時功耗僅有33 mW。

3.5 FPGA及存儲器

在一個以FPGA為核心的語音處理系統中,用存儲容量、存儲時間、回放音質等指標衡量語音處理系統優越性。系統選用FLASH作片外存儲器,實現語音數據的數字錄音和回放,既保證了系統的高性能,又降低了系統成本。三星公司產品K9F1G08UOM具有128 M×8 bit(1 Gbit)存儲容量,采用NAND閃存技術工藝,工作電壓2.7~3.6 V,功耗低,容量大,數據訪問速度高。

此芯片由8 192個塊(block)組成,每塊由32個頁(page)組成,每頁為512×8 bit。如果需要進行字節級訪問,128 Mbyte容量需要27根地址線,所以需要4個周期的地址輸入,依次是列地址(A0~A7)、低位行地址(A9~A13)、高位行地址(A14~A26),其中A8由00h和01h2種命令分別設置為低和高,以分別選擇每頁的前256Byte和后256Byte。如此設計I/O總線目的為:(1)減少芯片的管腳數量;(2)當系統需要更大容量的芯片時,可維持系統板級設計的一致性。

系統的A/D采樣速率設置在250 kHz左右,字長8 bit,1 s的語音數據需要8 Kbyte的存儲空間,而存儲器容量為128 Mbyte,所以1片可存儲9 min左右的語音數據。FPGA與A/D,D/A及存儲器的連接如圖4所示。

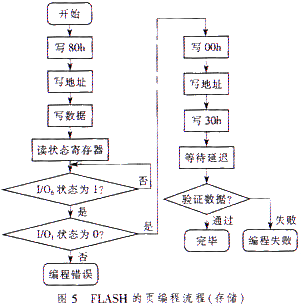

4 軟件設計

在錄音按鍵有效時,首先對FLASH 中的1 024進行塊擦除,然后對FLASH進行寫操作,此時才能往存儲器中寫數據,FLASH的頁編程流程圖如圖5所示。

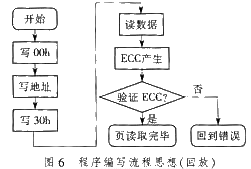

放音狀態有一個主要的程序即對FLASH的對操作,圖6為程序編寫流程圖,其中ECC為誤差糾正代碼。另外,程序中通過控制RE的低電平信號頻率來控制輸出數據的速率,實際程序中把頻率控制在250 kHz左右,與A/D的采樣頻率相同。

5 結束語

系統電路簡單,程序簡潔。采用FLASH存儲器保存語音數據,即使斷電仍能保持數據不丟失,保存數據安全可靠。如果在軟件中增加數據壓縮算法,可節省存儲空間,是一種實用的電路設計方案。

評論