基于PowerPC440GP型微控制器的嵌入式系統(tǒng)設計

1 引言

本文引用地址:http://www.104case.com/article/78877.htmPowerPC440GP是IBM公司推出的高性能32位RISC嵌入式處理器,片上集成了PowerPC440內(nèi)核及各種豐富的外圍設備接口資源,最高速度可達500 MHz,適合應用在嵌入式產(chǎn)品諸如交換機、路由器、網(wǎng)絡服務器等臺式設備中。本文針對該處理器的特點提出一種針對網(wǎng)絡服務器的較為通用的應用系統(tǒng)設計方案,并對此方案的關鍵軟硬件技術進行討論。

2 PowerPC440GP的特點與性能

128位處理器局部總線(PLB)可提供峰值為4.2GB/s的讀寫能力,用來訪問PCI,DDR SDRAM等高性能設備,采用36位地址路徑,能提供64 GB內(nèi)存尋址能力。

32位片上外圍設備總線(0PB)連接串口、以太網(wǎng)口、外部總線控制器、I2C口等低性能設備,以提高PLB總線利用率。

10位尋址的DCR總線訪問PLB總線上各種主從設備的狀態(tài)與控制寄存器。

擁有64位片上雙倍速率DDR SDRAM控制器,最多可提供4個設備片選信號。

擁有最高頻率133MHz的64位PCI接口。

可支持8個外設的32位外部總線控制器。

2個10 MB/s/100 MB/s片上以太網(wǎng)控制器。

2個串口和2個I2C口。

32個通用輸入輸出口GPIO。

13個外部中斷和45個內(nèi)部中斷資源。

CPU工作頻率可在400 MHz、466 MHz、500MHz頻率下通過初始化配置選擇,一般功耗小于4W。

電源:邏輯電壓為1.8 V,DDR SDRAM接口電壓為2.5V,I/O口電壓為3.3V。

3 應用系統(tǒng)設計方案

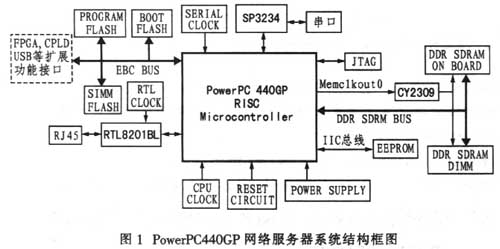

該網(wǎng)絡服務器平臺以PowerPC440GP為核心,進行了必要的擴展,系統(tǒng)結構框圖如圖1所示。

系統(tǒng)包含PowerPC440GP處理器及其上電復位電路、電源電路、系統(tǒng)時鐘電路、DDR內(nèi)存及擴展電路、程序存儲及啟動調(diào)試Flash電路,1個連接在I2C總線上提供啟動配置的EEPROM,用于ICE調(diào)試的JTAG口,以及以太網(wǎng)口、串口等通信接口。

3.1 電源電路設計

本系統(tǒng)共需1.8 V和2.5 V、3.3 V 3種電源,其中由開關電源為系統(tǒng)提供統(tǒng)一的3.3 V電源和地平面,選用LP3963ES-2.5型LDO提供2.5 V電壓,該電路的最大負載電流可達3 A,能滿足系統(tǒng)需要。以2.5 V為輸入,選用的TPS77518型DC/DC轉(zhuǎn)換器提供1.8 V電壓,可有效減少二次電源的功率損耗。

3.2 CPU時鐘電路設計

本系統(tǒng)采用一個33.33 MHz的外部晶體振蕩器連接到CPU的Sysclk引腳作為外部輸入的低頻時鐘源,然后通過初始化配置片內(nèi)鎖相環(huán)(PLL)將外部輸入的低頻時鐘源倍頻,為系統(tǒng)提供高頻系統(tǒng)時鐘。

3.3 DDR SDRAM電路設計

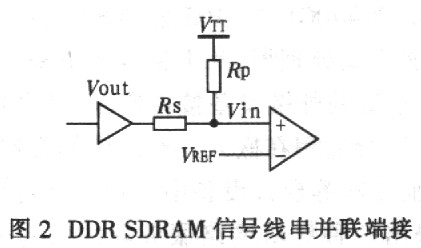

由于PowerPC440GP的DDR SDRAM接口具有最高64位數(shù)據(jù)總線和8位ECC糾錯位,所以選用5個HY5DU281622ETP-M作為板上內(nèi)存模塊,該電路結構為8 Mxl6 bits,5個內(nèi)存電路共用1個bankSel0片選空間,其中4個內(nèi)存電路構成數(shù)據(jù)總線為64位的數(shù)據(jù)存儲區(qū),內(nèi)存容量為64 M字節(jié),另外1個內(nèi)存電路的低8位用作ECC。還可擴展1個184針的DIMM(必須采用72位的ECC內(nèi)存條)。內(nèi)存模塊各電路及DIMM的時鐘由PowerPC440GP的Memclkout0引腳提供(其頻率等于PLB總線時鐘,一般為100 MHz或133 MHz)。為了保證各器件時鐘同步.引入CY2309時鐘匹配器件,該器件擁有內(nèi)部時鐘鎖相環(huán),可以將引腳輸出的時鐘信號分成9條相位頻率完全相同的時鐘信號(5條供給芯片,4條供給DIMM),并且可以避免任一時鐘信號反射對其他時鐘造成的影響。DDRSDRAM模塊采用SSTL-2信號標準,工作電壓為2.5 V。進行布板設計時要重點考慮Data/DM/DQS等信號線的走線及長度、信號線的端接方法及符合SSTL-2信號要求的端接電壓VTT和輸入?yún)⒖茧妷盒盘朧REF的電路設計。Data/DM/DQS等信號線應盡量采用相同的走線結構并嚴格保持等長。信號線末端的端接推薦使用串并聯(lián)方式,如圖2所示。這里串聯(lián)端接電阻器的阻值一般為22 Ω,并聯(lián)端接電阻器阻值一般為25 Ω,位置應盡量靠近信號接收端引腳,可有效減少信號反射和電磁干擾,適應更高的時鐘率。對于端接電壓VTT和參考電壓VREF,采用內(nèi)存廠商推薦的ML6554來提供。另外,由于DDRSDRAM電路時序操作的復雜性,結合控制器內(nèi)部時序寄存器的配置對這部分電路進行板級仿真是非常重要的。

3.4 程序存儲電路設計

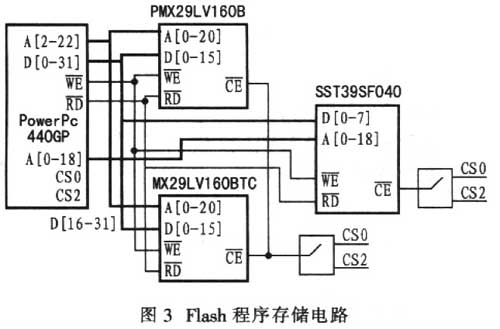

由于PowerPC440GP的EBC總線具有32位數(shù)據(jù)線,選擇2個MX29LVl60BTC型Flash器件用以存放BSP、實時操作系統(tǒng)VxWorks和用戶應用程序。將Flash的BYTE引腳設置為高電平,使Flash工作于x16模式。這樣2個Flash共用1個CS0片選空間,構成EBC數(shù)據(jù)總線同步訪問的高16位和低16位,容量為4M字節(jié)。由于PowePC440GP采用PowerPC內(nèi)核,即440GP的A31是LSB,A0是MSB,數(shù)據(jù)總線亦然,而Flash的A0和DO皆是LSB,連線時要注意引腳次序。另外,由于Flash是4字節(jié)同步讀取操作,連線時應將CPU的地址線左移2位,即最低位A0和Al不用。

為了便于系統(tǒng)調(diào)試,可增加1個512 KB的SST39SF040用于BootROM啟動,通過跳線與2個Flash互選CS0片選,這樣系統(tǒng)啟動時會自動從CSO的設備上讀取啟動代碼。程序存儲模塊如圖3所示。

3.5 以太網(wǎng)接口電路設計

用RTL8201BL型網(wǎng)口電路實現(xiàn)Power-PC440GP與100MHz以太網(wǎng)的接口,使用外部25MHz晶體振蕩器,通過16PT8515型網(wǎng)絡濾波器連接以太網(wǎng),如圖4所示。由于PowerPC440GP帶有100 MHz以太網(wǎng)MAC,所以能夠?qū)崿F(xiàn)和RTL820lBL的無縫連接。RTL8201BL有2種接口:SNI和MII,本系統(tǒng)采用MII。接口的選擇可以通過設置MII/SNIB引腳為高電平、正確設置ANE、SPEED和DUPLEX引腳來實現(xiàn)。MII能夠運行在25 MHz和2.5 MHz頻率,分別為100 MHz以太網(wǎng)和lO MHz以太網(wǎng)支持。數(shù)據(jù)傳輸時,MAC首先判定THEN信號并將8位數(shù)據(jù)改為4位數(shù)據(jù),再通過TXD[0:3]傳到物理層上,在TXEN信號有效期間,PHY通過傳輸時鐘信號TXCLK對TXD[0:3]上的數(shù)據(jù)進行同步采樣;接收數(shù)據(jù)時,PHY判定接收使能信號來接收RXD[0:3]上的數(shù)據(jù)。

3.6 系統(tǒng)啟動配置

PowerPC440GP有1個I2C總線啟動配置控制器。當引腳UARTO-DCD#被置為高電平時使能該控制器。選用1個保存有啟動配置信息的AT24C32連接到I2CO接口作為從設備。當系統(tǒng)上電或者復位時,該控制器能夠從位于I2C0接口的從設備中連續(xù)讀取16個字節(jié)。這16個字節(jié)數(shù)據(jù)被保存在4個上電配置寄存器CPC0-STRPO:3中,用來初始化PLL設置、片內(nèi)各總線時鐘率、啟動位置、啟動寬度及一些用戶定義的配置等。如果讀取數(shù)據(jù)失敗或者引腳UART0-DCD#被置于低電平,則這些配置將全部使用默認值。另一配置引腳UART0-DSR#置高電平或低電平?jīng)Q定了I2C總線從設備7位地址是0xA0還是0xA8。

4 VxWorks的開發(fā)與移植

本系統(tǒng)選用Windriver公司推出的嵌入式實時操作系統(tǒng)VxWorks及其集成開發(fā)工具Tornado。系統(tǒng)開發(fā)調(diào)試工具采用Windriver公司生產(chǎn)的Vision-Ice仿真器。仿真器一端連接PC網(wǎng)口,另一端連接PowerPC440GP的JTAG接口。開發(fā)時首先調(diào)試PowerPC內(nèi)核和外部DDR SDRAM,一旦工作正常,就可以通過仿真器下載RTOS到內(nèi)存來輔助硬件調(diào)試。然后調(diào)試網(wǎng)口,如果網(wǎng)口工作正常,就可以脫離仿真器,利用Tornado提供的工具軟件(例如WDB),通過網(wǎng)口線建立電路板與PC的通信機制,調(diào)試其他模塊和開發(fā)應用程序。開發(fā)程序完成后,將正確的啟動代碼燒制到BootROM中,由BootROM引導程序通過ftp將VxWorks內(nèi)核與應用程序下載燒制到Flash中。

VxWorks廣泛流行的重要原因是它的可移植性,通過板級支持包BSP,VxWorks操作系統(tǒng)的應用代碼可獨立于硬件。系統(tǒng)移植時只需根據(jù)硬件平臺修改BSP,不需要改變操作系統(tǒng)和應用程序。

5 VxWorks BSP文件結構與開發(fā)流程

在VxWorks中,BSP由一組與特定目標系統(tǒng)相關的文件組成。這些文件包括編譯文件makefile、ROM初始化文件romInit.s、系統(tǒng)初始化文件sysAlib.s、配置文件config.h、目標板定義文件bspname.h、網(wǎng)絡配置文件configNet.h、系統(tǒng)庫文件sysLib.c、用戶配置文件usrConfig.c、引導配置文件bootConfig.c、引導初始化文件bootlnit.C、串口文件sysSerial.c、以太網(wǎng)接口文件ibmEmacEnd.c等,BSP啟動流程如圖5所示。

5.1 建立開發(fā)環(huán)境

主要以開發(fā)板CPU的BSP文件為模板,在tornadotargetconfig目錄下創(chuàng)建用戶的BSP目錄bspname,把tornadotargetconfigall下的文件和BSP模板文件拷貝到該目錄下。

5.2 修改模板文件

5.2.1 makefile

該文件通過命令行方式對創(chuàng)建映像文件進行控制,必須定義下列宏:

CPU:PowerPC440GP;

TOOL:GNU;

TGT_DIR:目標板目錄的路徑,使用默認;

TARGET_DIR:BSP目錄名,自定義;

VENDOR:目標生產(chǎn)商名,IBM;

BOARD:目標板名,自定義;

ROM_TEXT_ADRS:啟動ROM的入口地址,本系統(tǒng)設為O×fff80100;

ROM_SIZE:ROM大小,本系統(tǒng)為512 KB;

RAM_LOW_ADRS:加載VxWorks的目標地址,本系統(tǒng)設為0x00010000;

RAM_HIGH_ADRS:將引導ROM映像復制到RAM中的目標地址,本系統(tǒng)設為0x00C00000。

5.2.2 BSPname.h

該文件根據(jù)PowerPC440GP設置串行接口、時鐘及I/O設備等,必須包含以下內(nèi)容:

中斷向量/優(yōu)先級別;

I/0設備地址;

設備寄存器各位的含義;

系統(tǒng)和附加時鐘參數(shù)(最大和最小速率)。

5.2.3 config.h

該文件包含定義所有與PowerPC440GP目標板相關的組件。

設置缺省啟動行

:使用網(wǎng)絡啟動;

RAM地址和大小:地址從0開始,64 MB大小設置ECC:使能;

設置是否支持MMU和Cache:支持Cache;

定時器是否使用外部時鐘:否;

串口時鐘定義:使用外部時鐘;

串口默認通道:使用通道1;

包含網(wǎng)口:支持以太網(wǎng)接口;

WDB默認通信方式:網(wǎng)口。

另外,注意ROM_TEXT_ADRS,ROM_SIZE,RAM_LOW_ADRS,RAM_HIGH_ADRS必須與makefile中的定義保持一致。

5.2.4 romInit.s

該文件是一端匯編語言的初始化代碼,其中的romInit()函數(shù)是BootROM和基于ROM的Vx-Works映像的入口。需要做的工作有:

將相關寄存器清零和置位;

屏蔽中斷:通過設置MSR寄存器中的CE位與EE位;

關閉數(shù)據(jù)、指令Cache;

初始化EBC總線寄存器:通過對bank寄存器的設置為EBC總線上的各種設備分配片選信號與地址空間;

初始化內(nèi)存:對DDR SDRAM接口各寄存器進行配置,為板載內(nèi)存與DIMM分配片選信號與地址空間。注意時序寄存器SDRAM0_TRl,SDRAM0_WRDTR等的配置應與內(nèi)存模塊的布線仿真結合起來;

初始化堆棧指針;

計算romStart()函數(shù)地址,然后跳轉(zhuǎn)到該函數(shù)執(zhí)行C語言代碼,并不再返回。

5.2.5 用戶配置文件usrConfig.c

其中的代碼是VxWorks映像的主要初始化代碼,而引導配置文件bootConfig.c中的代碼是bootrom映像的主要初始化代碼。bootInit.c是ROM初始化的第2階段,RomInit()完成后跳轉(zhuǎn)到此文件中的romStart(),該函數(shù)完成ROM映像所需要的解壓縮和重定位工作。以上3個文件一般無須用戶直接修改。

5.2.6 系統(tǒng)庫文件syslib.c

該文件包含與特定目標系統(tǒng)相關的庫函數(shù),這些函數(shù)為操作系統(tǒng)和應用程序提供板級接口,使這些程序與硬件系統(tǒng)無關。該文件至少包含下列函數(shù):sysModel,sysBspRev,sysHwInit,sysHwInit2和sys MemTop等,其中sysHwInit是本文件的核心,大部分硬件初始化工作都在這部分完成,本系統(tǒng)也可選擇將包括串口,網(wǎng)口等硬件設備的初始化入口程序添加到該函數(shù)中,相關設備的驅(qū)動程序可作為子文件引入syslib.c。

5.3 創(chuàng)建VxWorks映像

根據(jù)具體需要在命令行環(huán)境下利用makefile創(chuàng)建各種鏡像,也可以在Tornado集成環(huán)境下在Build菜單里選擇Build Boot Rom來創(chuàng)建各種類型的BootROM。

6 結束語

介紹了一種新型高性能嵌入式處理器,并對以這種處理器為核心構建的網(wǎng)絡服務器的硬件設計和軟件開發(fā)流程做了詳細說明。鑒于不同處理器的嵌入式系統(tǒng)設計具有一定的共性,本文可為其他類型的嵌入式系統(tǒng)開發(fā)提供一定的參考。

評論