ADI時鐘抖動衰減器優化JESD204B串行接口功能

Analog Devices, Inc.,全球領先的高性能信號處理解決方案供應商,最近推出一款高性能時鐘抖動衰減器HMC7044,其支持JESD204B串行接口標準,適用于連接基站設計中的高速數據轉換器和現場可編程門陣列(FPGA)。JESD204B接口專門針對高數據速率系統設計需求而開發,3.2 GHz HMC7044時鐘抖動衰減器內置可以支持和增強該接口標準特性的獨特功能。HMC7044提供50 fs抖動性能,可改善高速數據轉換器的信噪比和動態范圍。該器件提供14路低噪聲且可配置的輸出,可以靈活地與許多不同的器件接口。HMC7044還具有各種時鐘管理和分配特性,使得基站設計人員利用單個器件就能構建完整的時鐘設計。

本文引用地址:http://www.104case.com/article/279911.htm

查看產品頁面、下載數據手冊、申請樣片和訂購評估板:http://www.analog.com/pr150909/hmc7044

通過在線技術支持社區EngineerZone®聯系工程師和ADI產品專家: https://ezchina.analog.com/community/rf

更多有關產品信息,請致電亞洲技術支持中心:400 6100 006, 或發送郵件至 china.support@analog.com , 也可點擊ADI官方微博http://weibo.com/analogdevices ,或通過手機登錄m. analog.com 或 www.analog.com了解最新產品等信息。

更多ADI產品及應用視頻,請訪問:http://videos.analog.com/category/chinese/

基站應用中有許多串行JESD204B數據轉換器通道需要將其數據幀與FPGA對齊。HMC7044時鐘抖動衰減器可在數據轉換器系統中產生源同步且可調的樣本和幀對齊(SYSREF)時鐘,使JESD204B系統設計得以簡化。該器件具有兩個鎖相環(PLL)和重疊的片內壓控振蕩器(VCO)。第一PLL將一個低噪聲、本地壓控時鐘振蕩器(VCXO)鎖定至噪聲相對較高的參考,而第二PLL將VCXO信號倍頻至VCO頻率,僅增加非常小的噪聲。對于蜂窩基礎設施JESD204B時鐘產生、無線基礎設施、數據轉換器時鐘、微波基帶卡和其它高速通信應用,HMC7044架構可提供出色的頻率產生性能,相位噪聲和積分抖動均很低。

HMC7044時鐘抖動衰減器主要特性

支持JEDEC JESD204B

超低均方根抖動:50 fs(12 KHz至20 MHz,典型值)

噪底:-162 dBc/Hz (245.76 MHz)

低相位噪聲:<-142 dBc/Hz(800 kHz至983.04 MHz輸出頻率)

PLL2提供多達14路差分器件時鐘

支持最高5 GHz的外部VCO輸入

片內穩壓器提供出色的PSRR

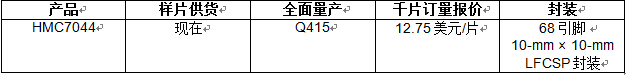

報價與供貨

評論