互連時序模型與布線長度分析

2.2 RMII接口

本文引用地址:http://www.104case.com/article/274626.htmRMII接口也是常用的百兆以太網PHY芯片與MAC間的接口。表5是某百兆PHY的時序參數表,表6和表7分別是某MPU內部MAC的時序參數表。

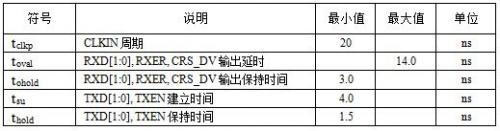

表5某PHY芯片的時序參數表

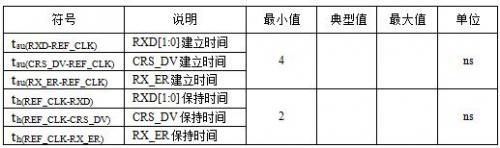

表6某MPU內MAC RX通道時序參數表

表7某MPU內MAC TX通道時序參數表

該MPU內MAC在RMII模式時,不支持時鐘輸出,同時PHY要求時鐘信號為輸入。該MPU配合PHY工作在RMII模式下,需要外部使用一顆符合雙方精度要求的50MHz振蕩器,來為雙方提供時鐘基準。

為簡化時序分析,可以將外部振蕩器至MPU和PHY雙方的走線設計為等長,此時時鐘信號在兩者的時鐘輸入引腳上具有完全一致的時刻。

注意:等長走線的一般實現方法是蛇形線,但等長的蛇形線并不一定意味著等延時。只有當蛇形線的延時效果等同或者盡可能近似于直線時,等長才意味著等延時。為了讓蛇形線具有類似于直線的延時效果,蛇形線的高度應盡可能小,蛇形線的開口應盡可能寬,也就是說,波浪線的外形更利于等延時。

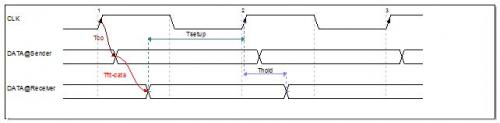

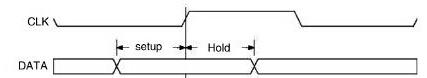

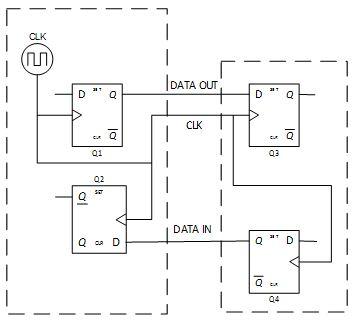

當時鐘信號等時刻到達收發雙方的輸入引腳時,具有如圖5所示的時序模型,因而僅需討論數據線的長度。

圖5共用時鐘的RMII時序模型

根據上述時序模型,可得出下列時序公式:

(Tsetup)min + (Tco)max + (Tflt-data)max + Tjitter-clk+ Tjitter-data (Thold)min(8)

對RXD、CRS_DV和RX_ER信號來說,該組信號由PHY發給MPU,根據公式(7)和公式(8),可得(為了簡化,認為最小的Tco時間等于Thold時間):

1 flt-data < 2

走線時間不可能為負值,假設走線位于PCB表層,材料為FR-4,則:

Lflt-data < 31.75CM

對TXD、和TX_EN信號來說,該組信號由MPU發給PHY,根據公式(7)和公式(8),可得:

-0.5 flt-data < 3

走線時間不可能為負值,假設走線位于PCB表層,材料為FR-4,則:

Lflt-data < 47.625CM

對RXD、CRS_DV和RX_ER信號來說,該組信號由PHY發給MPU。假設數據線走線長度為0,則數據線延時為0ns,此時在MPU側接受到信號的最小建立時間為:20-14=6ns,最小保持時間為:3ns。MAC側要求的最小建立時間為4ns,最小保持時間為2ns。可見,此時數據線的走線長度最長延時可以到2ns,此時MAC側接受到信號的建立時間和保持時間分別為4ns和5ns,符合時序要求。所以走線長度最長可以為31.75CM。

對TXD和TX_EN信號來說,該組信號由MPU發給PHY。假設數據線走線長度為0,則數據線延時為0ns,此時在PHY側接受到信號的最小建立時間為:20-13=7ns,最小保持時間為:2ns。MAC側要求的最小建立時間為4ns,最小保持時間為1.5ns。可見,此時數據線的走線長度最長延時可以到3ns,此時MAC側接受到信號的建立時間和保持時間分別為4ns和4.5ns,符合時序要求。所以走線長度最長可以為47.625CM。

3.結論

進行時序分析的關鍵點首先在于必須對被分析的時序關系非常清楚、能夠深刻理解當前對象的時序協議。其次,時序分析要針對具體問題具體分析,不存在所謂的萬能時序公式。有時,單純依靠理論分析或者單純依靠時序關系公式并不一定能夠解決問題,而是要兩者結合使用。

對于高速信號的布線而言,存在“等長”說,即很多工程師認為只要所有的線路盡可能等長,就一定滿足時序要求。事實上,這是一種錯誤的認識,本文的實例分析就明確證明了這一點。只有那些時鐘和數據由同一個器件發出,由另一個器件接受,并且發送端的建立時間和保持時間恰好滿足接收端需求時,“等長”才算是一種偷懶的方法。除此以外,尤其是那些通過單向時鐘驅動、采樣雙向數據或者逆向數據的信號,必須具體問題具體分析。當然,對于PC機這類通用設備來說,由于主板的設計需要兼容不同廠家的內存條,此時走線設計為等長確實是合理的設計。

公共時鐘系統由于使用單向時鐘信號對雙向數據進行采樣,因此存在雙重限制,兩組限制制約了走線不僅有走線長度差值限制,同時還有走線總長度限制。源同步時鐘系統使用與數據同向的時鐘,因此只存在單重限制,使得走線只有差限制而沒有總長度限制。

一般而言,對于SPI接口、MII接口、共享時鐘的RMII接口或者SDRAM信號,走線應盡可能的短。對于DDR SDRAM信號以及RGMII等DDR時序的接口來說,多數情況下,組內等長確實是一種簡便快速的方法。

評論