LEON2應用于DCPU的FPGA仿真

0 引言

本文引用地址:http://www.104case.com/article/273881.htm近年來,隨著數字多媒體業務和Internet網絡的迅速發展,新型數字機頂盒可以有效利用我國巨大的有線電視網絡資源,完成視頻點播、數字電視的接收及接入Internet等綜合業務功能。

1 數字機頂盒總體設計方案

數字機頂盒分為兩個通道,下行通道接收來自電纜或光纖的有線電視信號,上行通道傳輸從客戶端到服務器端的指令。

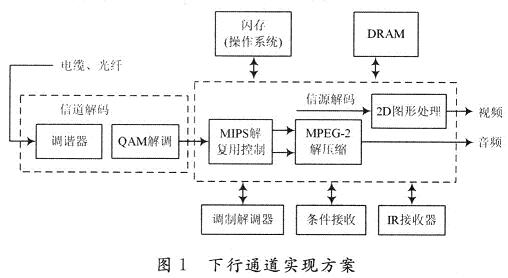

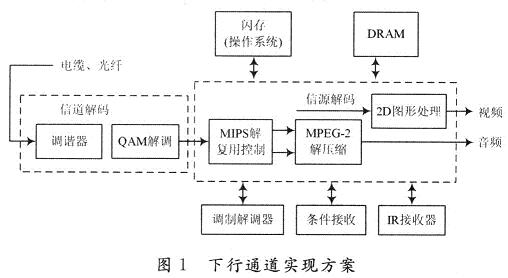

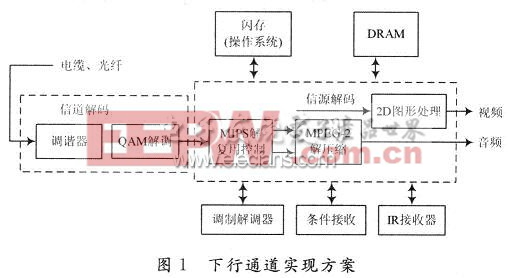

下行通道方案如圖1所示,調諧器接收來自有線網的高頻信號,通過QAM解調器完成信道解碼,從載波中分離出包含音、視頻和其他數據信息的傳送流(TS)。傳送流中一般包含多個音、視頻流及一些數據信息。解復用器則用來區分不同的節目,提取相應的音、視頻流和數據流,送入MPEG一2解碼器和相應的解析軟件,完成數字信息的還原。對于付費電視,條件接收模塊對音、視頻流實施解擾,并采用含有識別用戶和進行記賬功能的智能卡,保證合法用戶正常收看。MPEG一2解碼器完成音、視頻信號的解壓縮,經視頻編碼器和音頻D/A變換,還原出模擬音、視頻信號,在常規彩色電視機上顯示高質量圖像,并提供多聲道立體聲節目。

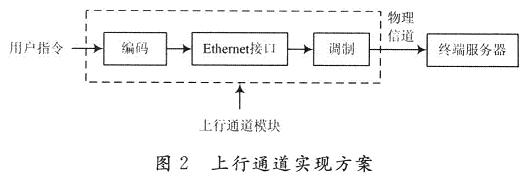

上行通道方案如圖2所示,用戶發送指令,然后經過編碼符合網絡通信協議,從以太網接口傳輸到調制器,再經物理信道傳給終端服務器。

2 LEON2處理器

嵌入式CPU是數字電視機頂盒的心臟,當數據完成信道解碼以后,首先要解復用,把傳輸流分成視頻、音頻,使視頻、音頻和數據分離開。CPU是嵌入式操作系統的運行平臺,它要與操作系統一起完成網絡管理,顯示管理、有條件接收管理、圖文電視解碼、數據解碼、視頻信號的上下變換等功能。

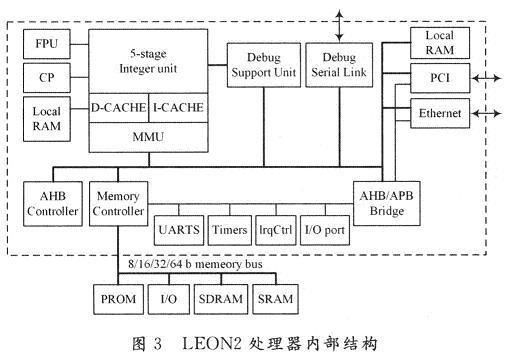

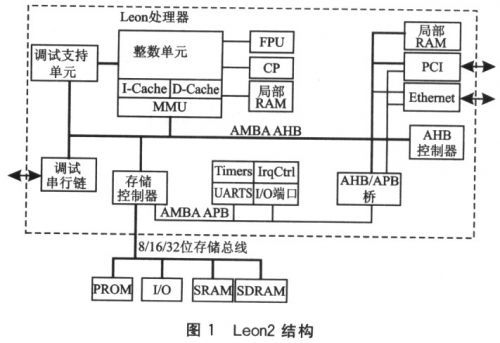

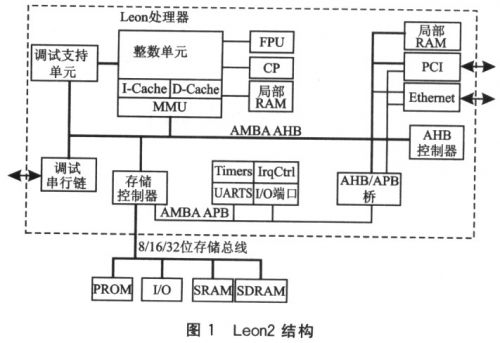

LEON系列32位RISC處理器核的第一個版本是LEONl,它是由歐洲航天局主持設計開發的。LEONl的設計初衷是為了使歐洲能夠擺脫在航空航天高性能嵌入式處理器上對美國的嚴重依賴。以Jiri Caisler為首的設計團隊在完成LEONl后從歐洲航天局獨立出來,成立了Gaisler Research公司,后來就推出了LE—ON2處理器。LEON2是一個可配置的微處理器核,使用SPARC V8指令集,它的源代碼由可綜合的VHDL代碼構成。LEON2內部結構如圖3所示。

fpga相關文章:fpga是什么

評論