FPGA系統設計的仿真驗證之:SDRAM讀寫控制的實現與Modelsim仿真

(4)操作控制。

本文引用地址:http://www.104case.com/article/273721.htmSDRAM 的具體控制命令由一些專用控制引腳和地址線輔助完成。CS、RAS、CAS 和WR 在時鐘上升沿的狀態決定具體操作動作,地址線和Bank選擇控制線在部分操作動作中作為輔助參數輸入。

由于特殊的存儲結構,SDRAM 操作指令比較多,不像SRAM 一樣只有簡單的讀寫,具體操作指令如表7.3所示。

表7.3 SDRAM命令真值表

功 能命 令 字CSRASCASWEBAA10A[0:9]

取消器件選擇DSELHXXXXXX

無操作NOPLHHHXXX

讀操作READLHLHVLV

讀等待/自動預充電READAPLHLHVHV

續表

功 能命 令 字CSRASCASWEBAA10A[0:9]

寫操作WRITELHLLVLV

寫等待/自動預充電WRITEAPLHLLVHV

Bank激活ACTLLHHVVV

對指定Bank預充電PRELLHLVLX

對所有Bank預充電PALLLLHLXHX

自動刷新CBRLLLHXXX

加載模式寄存器MRSLLLLVVV

由表7.3可以看到,雖然SDRAM的容量大、速度快,但是存在存儲操作困難的問題。一般的解決方案有兩種,一是直接控制SDRAM的讀寫時序實現數據的存儲和讀取,二是編寫一個SDRAM的讀寫控制器,將SDRAM的讀寫簡化成SRAM形式,通過幾個命令完成SDRAM的讀寫。

3.SDRAM讀寫控制器

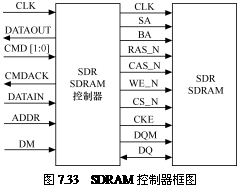

Xilinx、Altera、Lattice等較大的FPGA制造廠商都編寫了自己的SDRAM接口控制器。讀者可以到官方網站去申請相關的控制器源代碼。下面簡單介紹其中一種,如圖7.33所示是該SDRAM控制器總體設計框圖和外部接口信號。

在圖7.33中,控制器右端接口信號均為直接與SDRAM 對應管腳相連的信號,在表7.2中已做介紹,不再重復。

控制器左端的接口信號為與FPGA 相連的系統控制接口信號,定義如下。

· CLK:系統時鐘信號。

· ADDR:系統給出的SDRAM 地址信號。

· DATAIN:系統用于寫入SDRAM 的數據信號。

· DATAOUT:系統用于從SDRAM讀出的數據信號。

· CMD[1:0]、CMDACK:系統和控制器的命令交互信號,參見表7.3。

· DM:數據Mask信號。

一般來說,SDRAM的讀寫控制時序可以分為初始化、寫寄存器、自動刷新、突發模式讀、突發模式寫、整頁讀以及整頁寫等主要操作。具體的時序圖可以查閱相關的器件數據手冊,這里不再列出。

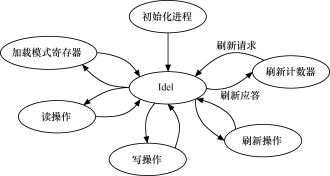

SDRAM的讀寫控制也可以由如圖7.34所示的讀寫狀態機表示。

在FPGA中,實現如圖7.34所示的狀態機,再利用已有的SDR SDRAM控制器即可實現對SDRAM器件的控制。

圖7.34 SDRAM讀寫狀態機

7.6.3 SDRAM控制器的Modelsim仿真

(1)打開ModelSim軟件。

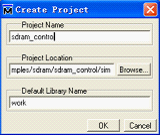

(2)創建工程。

如圖7.35所示,在Modelsim中創建新工程,并設置工程的相關屬性。

圖7.35 創建工程

(3)添加設計輸入。

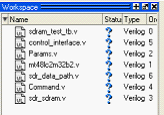

若要創建新的文件就選擇【Create New File】圖標,若要添加已經存在的文件就選擇【Add Existing File】圖標,如圖7.36所示。本實例中使用已經存在的SDRAM控制器源文件作為設計輸入,添加后,在Workspace瀏覽器中可以看到如圖7.37的設計輸入列表。

圖7.36 添加設計輸入 圖7.37 SDRAM設計輸入列表

(4)編譯設計輸入。

如圖7.38所示,在任意一個源文件上單擊右鍵,選擇“Compile”/“Compile All”,對所有的源文件進行編譯。

編譯后,若有錯誤,Modelsim會在信息欄中顯示出來。這時只要雙擊該錯誤,ModelSim就會自動打開該錯誤所在的文件,并定位到出現錯誤所在的位置附近。若編譯正確通過,源文件后面的藍色問號就替換成為綠色的對號,如圖7.39所示。

評論