ARM CortexA-72處理器:何來3.5倍性能

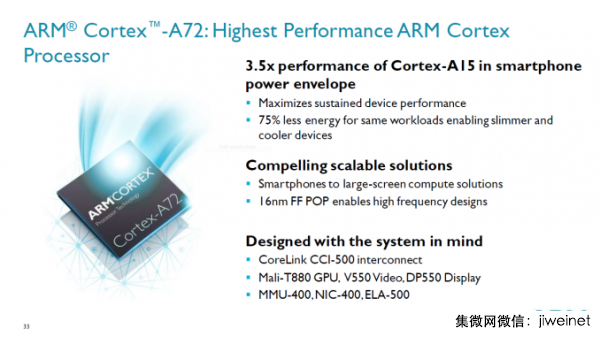

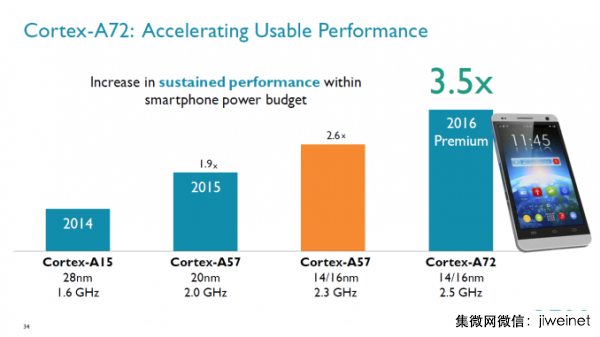

ARM雖然是家小公司,但他們是整個ARM處理器陣營的核心,除了蘋果、高通等極少數可以自己開發ARM兼容架構的公司之外,聯發科、海思等大多數公司都 會直接使用ARM的公版Cortex-A架構授權。64位時代以來,ARM已經發布了Cortex-A57/A53一大一小兩種架構,但只有A53遍地開花,高性能的A57核心在手機市場只有三星、高通在用,面臨著難產的尷尬。為此,ARM公司今年2月份推出了A57的繼任者——Cortex-A72架 構,號稱性能是A15的3.5倍,功耗則降低了75%。

本文引用地址:http://www.104case.com/article/273156.htm

當時我們對ARM的Cortex-A72核心了解并不多,只知道A72核心會使用新一代的FinFET工藝生產,包括三星/Globalfoundries的14nm及TSMC的16nm,得益于先進的工藝,A72核心頻率更高,可以達到2.5GHz,更高的頻率有助于A72增強服務器市場的存在感,這也是它的目標市場之一。

ARM日前公布了Coretx-A72核心的詳細架構,Anandtech網站也做了一番解析,我們來看下A72架構到底有哪些改進,畢竟A72核心很可能成為明年的旗艦手機/平板的標配。

值得一提的是,原先首先解釋了A72核心的命名由來,為什么不選擇Cortex-A59這樣的命名呢?ARM解釋說這純粹是方便市場宣傳而已,如果跟A57的命名很相近,那么大家就不容易看出這兩種核心之間的區別(大家都只會看數字辯好壞嗎?)。

A72核心的性能達到了A15的3.5倍

功耗降低了75%

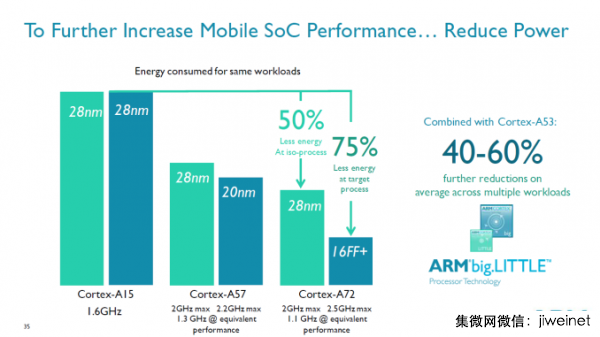

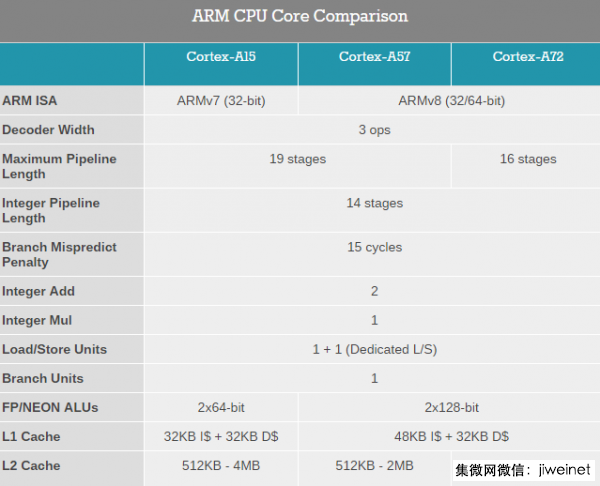

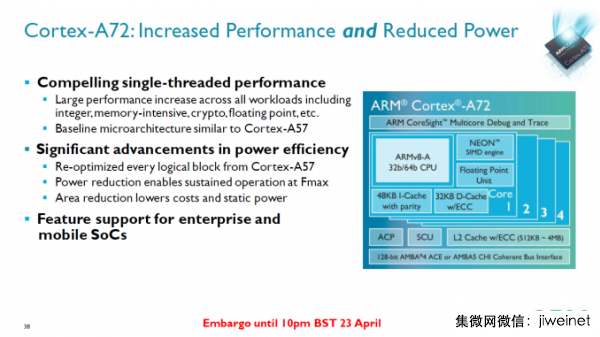

ARM之前宣傳A72核心性能是前代的3.5倍,功耗降低了75%,但大家也得清楚這只是宣傳而已,ARM并沒有直接對比A57與A72的差別,如果只看這兩者,A72核心在同樣的14/16nm工藝下只比A57提升了34%(2.6x到3.5x,還得考慮到頻率上的差異),而在同樣的28nm工藝下,其功耗也不過減少了20%左右。

還要注意到,A72核心可以運行在更高的頻率下,這不是簡單地最高頻率,此前A57由于太強,因此它只能在最高頻率下維持很短時間就要降頻,而ARM提供的數據表明,A72核心在16nm FinFET工藝下,2.5GHz頻率運行時功耗只有750mW。

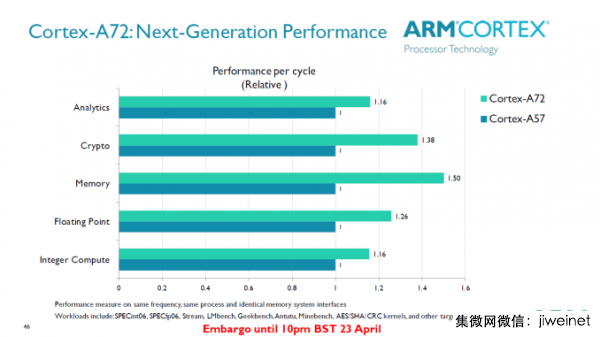

除了功耗之外,ARM還在A72架構上做了很多優化,如上圖所示,整數、浮點、內存等性能皆有不同程度的提升,雖然還缺少一些細節,不過IPC性能上提升16-30%還是有的。

由A57升級而來的A72架構

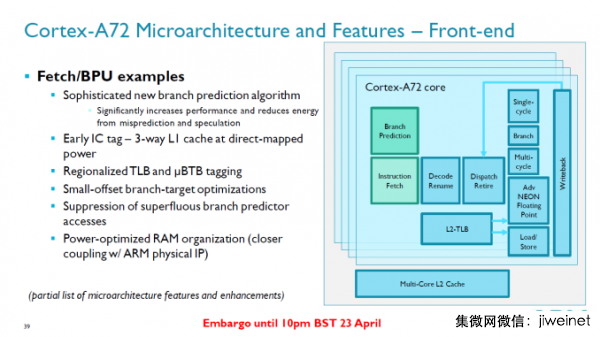

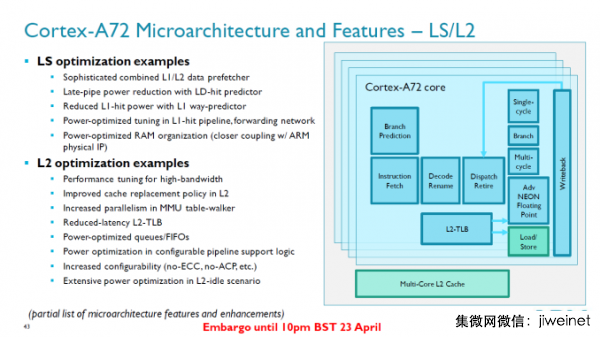

ARM似乎在性能、功耗及核心面積這三個方面都做了全面的改善,這也是半導體設計的三個重要指標。這個成績是ARM重新優化了幾乎所有A57邏輯區塊之后才得來的,其中CPU架構做了相當大的改進,包括新的分支預測單元,改善了解碼器管線設計等。

在指令預取這一塊,我們可以看到ARM重新設計了分支預測單元,它可以支持更復雜的算法,提高了性能、降低了功耗以、誤預測率及投機(speculation),具體來說就是相比A57降低了50%的誤預測,25%的投機率。多余的分支預測單元則被禁止了。——實際工作中,如果分支預測單元不能有效工作,那就會被繞過去。

此外,通過更好地耦合不同的IP模塊,ARM還優化了RAM組織。

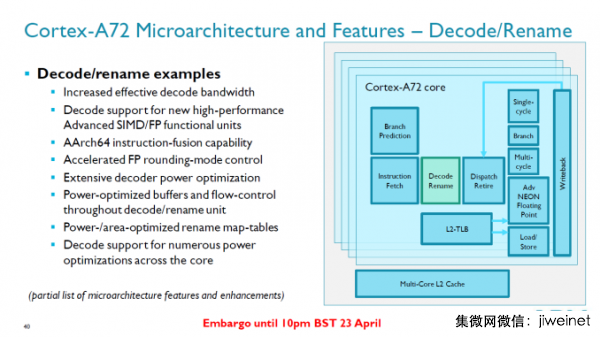

再來看A72的管線設計,解碼/重命名性能也提升了。解碼器自身是3指令發射的解碼器,但ARM在提升性能。降低功耗方面花了很大精力。為了提高要性能,提升了有效的解碼帶寬,而解碼器也獲得了一些AArch64指令融合增強。此外,功耗也通過多種方法降低了,包括直接的解碼等。

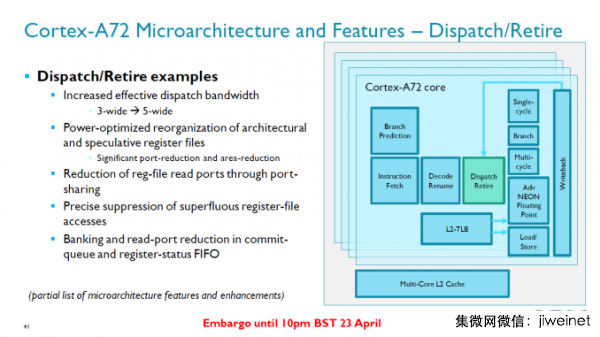

看起來指令分派/收回(Dispatch/retire)單元是提升性能而做的改進中變化最大的。解碼器可以融合指令,ARM的指令分派單元可以將ops操作打亂成更小的微操作(micro-ops)輸送給執行單元,這樣可以在指令派發單元將3發射變成等效5發射。這將提高解碼器的吞吐量,同時也提高了每個周期內指令派發單元創建的微操作數。

A72架構,ARM表示平均每個指令有1.08個微操作,這將緩解57架構中實際受限的指令派發單元的性能。

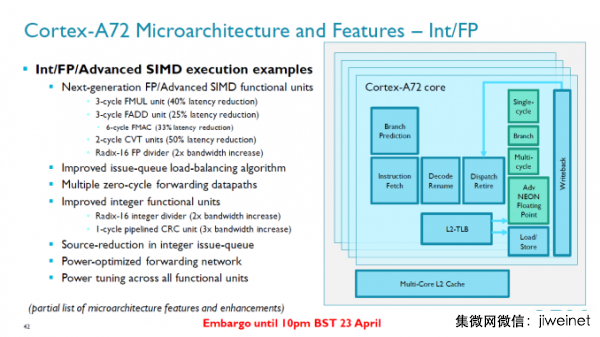

另一方面執行單元也有新的設計,包括新一代的FP浮點/高級SIMD單元,由于FP浮點管線從9降低到了6,因此延遲更低。FMUL(浮點乘法)的延遲也從5周期降低了3周期,FADD(浮點加法)從4降到3,FMAC(浮點累積乘)從9降低到6,CVT單元從4降到2。FP浮點單元的渲染管線長度從19降低到了16。

整數單元也做了改進,Radix-16除法器的帶寬加倍,CRC單元延遲降低到了1周期,相比A57架構其帶寬達到了3倍。

另一個重大的性能改進是L/S(Load/Store)單元,ARM表示L/S單元的帶寬提升了30%,這是因為引入了新的預取器。

A72架構紙面上的改進讓人印象深刻,它是A57架構的革新升級,不論是性能還是功耗,或者核心面積,A72都有改進。A57架構是去年Q3季度進入市場的,但現在才有三星、高通的A57架構處理器量產上市,所以A72核心真正進入市場還需要至少1年時間。

cvt相關文章:cvt原理

評論