冗余時鐘的平滑時鐘切換——電子設計

摘要:

本文引用地址:http://www.104case.com/article/271856.htm檢測到時鐘丟失時平滑切換到冗余時鐘源有助于避免系統運行中斷。

正文:

當今許多數據通信、網絡和計算機系統都需要實現時鐘冗余。組件或板級故障甚至簡單的定期系統維護等引起的任何中斷都不應造成系統運行中斷。因此,為整個電路工作提供時序的系統時鐘必須避免因任何異常情況而中斷。帶冗余的理想時鐘發生器也必須能在檢測到時鐘錯誤或丟失的情況下從母時鐘源平滑切換到子時鐘源或晶振。

以下給出幾類常用的冗余時鐘方案,其中包括:

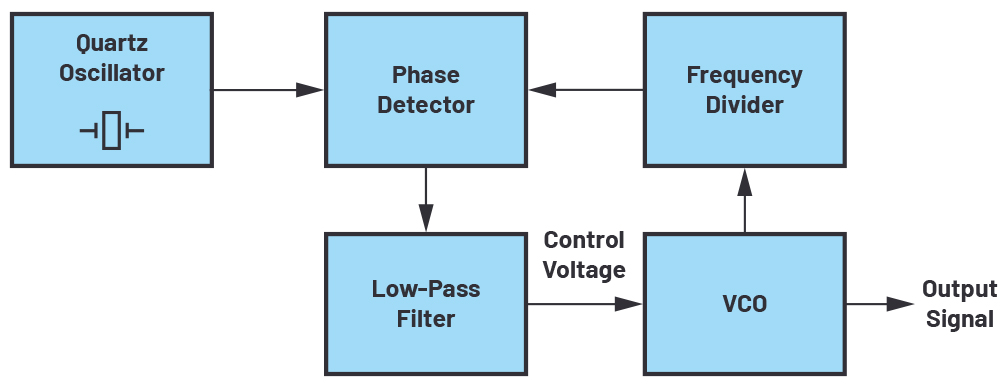

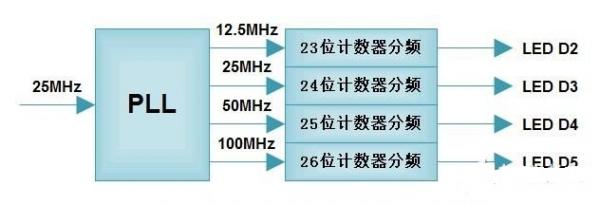

動態時鐘切換:根據這種方案,系統在檢測到母時鐘源丟失或錯誤的情況下可自動切換到子時鐘源。這種架構必須配備基于VCO的PLL。動態時鐘切換要求:(1)具備錯誤或丟失參考時鐘檢測器,以及(2)要求電路能順利無誤地切換到子時鐘源。

基于DCXO的時鐘切換:根據這種方案,數控晶體振蕩器(DCXO)可在母參考時鐘源存在或丟失時提供時鐘源。在存在參考時鐘的情況下,DCXO會保持對參考時鐘的PLL鎖定。而在參考時鐘丟失的情況下,DCXO則會通過保持參考時鐘的最后相位和頻率狀態來提供時鐘。

動態時鐘切換與基于DCXO的時鐘切換的對比

基于PLL的動態時鐘切換是一種切實可行的時鐘切換方式,這種操作方式可實現時鐘之間的平滑切換。在時鐘切換期內,會有單位周期相位校正(PCC)填入(或消除)母參考時鐘和子參考時鐘之間的相位差。母時鐘源和子時鐘源之間可能存在較大的相位誤差,這會造成在切換時間不夠長的情況下輸出時鐘出現較大相位沖突。基于PLL的器件應能夠通過延長切換時間讓單位周期相位校正(PCC)保持較小值,進而最大限度地減少相位沖突。PCC值的選擇必須足夠小,使其在切換期內不會對下游PLL或同步系統的設置/保持時間造成不利影響。

基于DCXO的時鐘切換方案采用可牽引晶振鎖相到參考時鐘。DCXO在母時鐘故障的情況下可保存參考時鐘最后的頻率和相位信息,從而有助于完成持續無誤的操作。當參考時鐘恢復時,DXCO能夠自動與該時鐘重新實現同步。基于DXCO的時鐘切換相對于動態時鐘切換而言可能具有一定的優勢,但同時也存在自身的不足:

1. 需要外部可牽引晶振。這種類型的晶振通常尺寸較大,需占用更多PCB面積;

2. 由于晶振牽引范圍有限,因此頻率鎖定范圍也有限。這就導致基于DXCO的標準器件的最大頻率變化限制為+/- 200PPM左右;

3. 速度太慢。DCXO PLL響應性使參考切換時間僅局限于數百毫秒(ms)的水平上;

4. 切換電容陣列會使頻率單獨改變,這就導致出現低頻相位沖突。覆蓋參考時鐘全部PPM變化的電容陣列數量有限(典型設計中只有10個)。由于DCXO輸出相位噪聲(或相位沖突)過大,設計人員不愿在高性能應用中使用這種器件;

5. 由于器件的架構特性,當存在良好參考時鐘時,輸出時鐘會在此期間顯出DCXO不盡人意的相位噪聲(或相位沖突)特性,而在參考時鐘暫時丟失的情況下,倒能提供干凈的晶振輸出頻率。這是因為參考時鐘丟失時,DCXO仍能保持參考時鐘的最后相位和頻率狀態且沒有任何更新,因此也就不存在相位沖突;

6. 基于DCXO的器件的PLL帶寬低(近2KHz)會造成跟蹤誤差過大;

7. 該器件因其PLL帶寬低而不具備擴頻意識。

基于DCXO的架構的低帶寬有一定的優勢,尤其是在參考時鐘切換時表現尤為突出。在母參考時鐘丟失而器件正被切換到子參考時鐘或晶振期間,較長的切換時間會使單位周期相位校正(PCC)值極小,從而有可能實現平滑的時鐘切換。理想的平滑時鐘切換器件應當是具有低PCC值的基于PLL的動態時鐘切換,或許需要時鐘切換時PLL能夠將帶寬從額定值1 MHz降至5-10 KHz的水平。利用這種可變的PLL帶寬架構,我們能夠實現平滑的時鐘切換。

參考時鐘和晶振之間的動態切換

基于PLL的動態時鐘切換可能不只能在參考時鐘之間實現,還可在參考時鐘和晶振輸入之間實現。在檢測到時鐘錯誤或丟失的情況下,VCO能夠切換到晶振輸入。只要平滑完成切換,這在功能上就與故障安全器件相同,只是它不會存在任何基于DCXO的器件的缺點,特別是上述第5點提及的問題。在這種情況下,既不需要可牽引晶振,也不會出現相位沖突問題。

單位周期相位校正(PCC)實現平滑切換

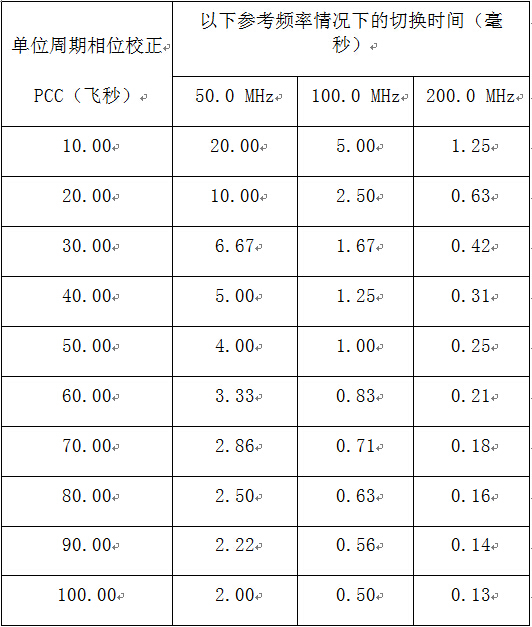

表1給出了50MHz、100MHz和200MHz等參考頻率下計算得出的不同單位周期相位校正的切換時間。這里,我們假定相同頻率但180°反相的兩個參考時鐘之間進行切換。不同參考頻率下的單位周期相位校正(PCC)和切換時間曲線變化如圖1所示。

表1:不同參考頻率下切換時間和單位周期相位校正的對比情況

從上圖可以看出,單位周期相位校正(PCC)和時鐘切換時間曲線呈指數變化。PCC值越大,切換時間就越短。而PCC值越小,切換時間則呈指數級增加。請注意,我們就該曲線圖做了如下假設:(a)PLL為線性相位錯誤校正,(b)PLL響應是在理想狀態下,沒有過沖或下沖。而在現實情況下,切換時間會比這里顯示的要長,而且很大程度上取決于PLL系統響應。此外,我們還要注意,PCC值不變的情況下,時鐘頻率越高,切換時間會越短。

基于DCXO的故障安全器件實際系統應用的經驗數據顯示,20飛秒的PCC足以滿足100-200 MHz頻率范圍的數據通信應用需求。在PCC為20飛秒的情況下,時鐘切換造成的相位沖突微不足道,不會對系統性能造成不利影響。為此,我們建議50 MHz的參考時鐘應采取的方案為20飛秒的PCC對應10 ms的切換時間。

動態平滑切換器件的設計通常包括兩個功能塊,如下所述:

1. 丟失參考時鐘或錯誤相位誤差檢測器電路:這將提供錯誤輸出,顯示正在啟動時鐘切換。必須規定用復位輸入引腳對錯誤輸出進行復位。

2. 參考時鐘切換電路:檢測到錯誤后,電路將被切換到子參考時鐘。子參考時鐘可以是外部時鐘源,也可以是晶振。在切換時間內,必須降低PLL帶寬以實現平滑切換。

本文介紹了冗余時鐘發生器源實現平滑時鐘切換的不同方法,以及不同冗余時鐘發生器的優劣勢。基于PLL的動態時鐘切換可平滑無誤地實現時鐘切換,建議使用該方法。動態時鐘切換的關鍵要求是,應特別注意單位周期相位校正(PCC)的問題。在檢測到時鐘錯誤或丟失情況下,以上建議的動態時鐘切換的獨特特性能夠實現從母時鐘源到子時鐘源或晶振的平滑時鐘切換。

參考資料:

http://www.cypress.com/?rID=12622 – 了解賽普拉斯的零延遲緩沖器

http://www.cypress.com/?mpn=CY23FS04ZXI – 賽普拉斯的DCXO產品系列

負離子發生器相關文章:負離子發生器原理 晶振相關文章:晶振原理 離子色譜儀相關文章:離子色譜儀原理

評論