基于SOPC技術(shù)的多通道實時溫度采集系統(tǒng)

2.4 FPGA邏輯控制模塊

本文引用地址:http://www.104case.com/article/271262.htm基于FPGA的采集控制單元,采用自頂而下的模塊化設(shè)計方法,使用Verilog HDL語言完成各控制模塊的設(shè)計。FPGA邏輯控制模塊包括A/D采樣控制模塊、FIFO讀寫控制模塊和SPC3控制模塊。

2.4.1 A/D采樣控制模塊

A/D采樣控制模塊負責控制外部ADS8402芯片多路模擬輸入量的選通,并實現(xiàn)對A/D采樣過程的合理控制。

由于ADS8402對16通道的模擬量采取分時轉(zhuǎn)換的方式,因此在啟動轉(zhuǎn)換的同時還要進行通道選擇。ADS8402設(shè)置了4根通道地址線A0、A1、A2、A3,以及地址鎖存允許信號ALE.當ALE變高時,鎖存由A0、A1、A2、A3編碼所確定的通道號,將該通道的模擬量接入A/D轉(zhuǎn)換器進行轉(zhuǎn)換。依據(jù)這樣的特性,設(shè)計一個帶復位端的十六進制計數(shù)器,其計數(shù)輸出端Q3、Q2、Q1、Q0分別與ADS8402的4根地址線相連。計數(shù)器上電復位以確保系統(tǒng)從0號通道開始采樣。將ADS8402的轉(zhuǎn)換結(jié)束信號EOC作為計數(shù)器的時鐘信號,實現(xiàn)一路轉(zhuǎn)換結(jié)束后自動啟動對下一路模擬輸入的采樣控制。

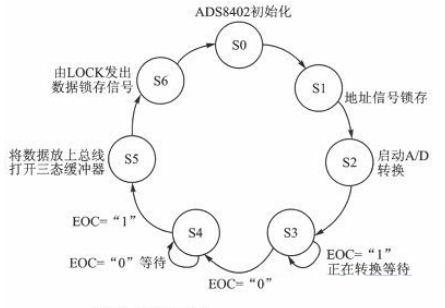

圖2 ADS8402采樣控制狀態(tài)轉(zhuǎn)換圖

A/D采樣過程的控制采用有限狀態(tài)機來實現(xiàn),把某一通道的采樣過程劃分為7個狀態(tài),如圖2所示。首先S0狀態(tài)對各個控制信號進行初始化。在S1狀態(tài)產(chǎn)生ALE信號的上升沿,鎖存通道地址。啟動信號START應在產(chǎn)生ALE信號的同一時鐘下降沿產(chǎn)生,由于VHDL語言在同一進程內(nèi)不允許時鐘的兩個沿作為敏感變量,所以將產(chǎn)生START信號單列為一個狀態(tài)S2,啟動轉(zhuǎn)換。在啟動轉(zhuǎn)換后,ADS8402使EOC置為低電平,設(shè)置S3狀態(tài)等待A/D轉(zhuǎn)換結(jié)束。轉(zhuǎn)換結(jié)束后,EOC信號由低電平轉(zhuǎn)換為高電平,狀態(tài)機進入S4狀態(tài),開啟輸出允許OE.狀態(tài)機進入S5狀態(tài),開啟數(shù)據(jù)鎖存信號LOCK鎖存數(shù)據(jù)。為產(chǎn)生與其他進程通信的信號,狀態(tài)機設(shè)置S6作為最后一個狀態(tài),然后跳轉(zhuǎn)回SO初始狀態(tài)。

2.4.2 FIFO讀寫控制模塊

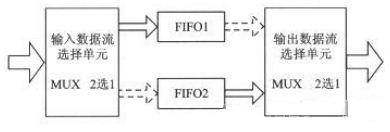

采用2片F(xiàn)IFO輪流讀寫操作,實現(xiàn)FPGA與PC機之間的數(shù)據(jù)緩存。乒乓傳輸控制原理示意圖如圖3所示,圖中的實線箭頭與虛線箭頭分別代表不同的讀寫數(shù)據(jù)周期。輸入數(shù)據(jù)流通過輸入數(shù)據(jù)流選擇單元,等時地將數(shù)據(jù)流分配到FIFO1、FIFO2中。在第1個緩沖周期,將輸入的數(shù)據(jù)流緩存到FIFO1.在第2個緩沖周期,通過輸入數(shù)據(jù)流選擇單元的切換,將輸入的數(shù)據(jù)流緩存到FIFO2,與此同時,將FIFO1緩存的第1個周期的數(shù)據(jù)通過輸出數(shù)據(jù)流選擇單元的選擇,送到數(shù)據(jù)流運算處理模塊被運算處理。在第3個緩沖周期,通過輸入數(shù)據(jù)流選擇單元的再次切換,將輸入的數(shù)據(jù)流緩存到FIFO1,與此同時,將FIFO2緩存的第2個周期的數(shù)據(jù)通過輸出數(shù)據(jù)流選擇單元的切換,送到數(shù)據(jù)流運算處理模塊被運算處理。如此循環(huán),周而復始。

圖3 FIFO乒乓傳輸控制原理

2.4.3 SPC3控制模塊

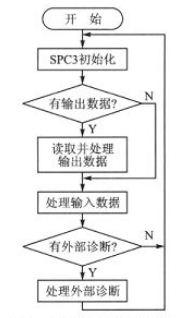

由于SPC3集成了完整的DP協(xié)議,因此在進行通信時,F(xiàn)PGA不用參與處理DP狀態(tài)機。主要任務是根據(jù)SPC3產(chǎn)生的中斷,將SPC3接收到的數(shù)據(jù)轉(zhuǎn)存,組織要通過SPC3發(fā)給的數(shù)據(jù),并根據(jù)要求組織外部診斷。在SPC3正常工作之前,需要進行初始化,以配置需要的寄存器,包括設(shè)置協(xié)議芯片的中斷允許,寫入從站識別號和地址,設(shè)置SPC3方式寄存器,設(shè)置診斷緩沖區(qū),配置緩沖區(qū)、地址緩沖區(qū)、初始化長度,并根據(jù)以上初始值得出各個緩沖區(qū)的指針和輔助緩沖區(qū)的指針。通信模塊的控制流程如圖4所示。

圖4 通信模塊控制流程

3系統(tǒng)的FPGA實現(xiàn)

3.1 Nios II系統(tǒng)架構(gòu)設(shè)計

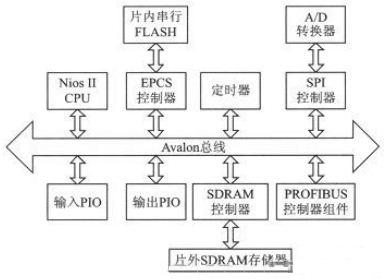

Nios II系統(tǒng)模塊包含:Nios II處理器、Avalon總線、并行輸入/輸出口PIO、串行外圍設(shè)備接口SPI、定時器Timer、片內(nèi)存儲器EPCS、片外存儲器SDRAM、PROFIBUS-DP的客戶定制邏輯。由Nios II處理器完成程序控制,主要負責對溫度的采集與數(shù)據(jù)存儲操作,并控制PROFIBUS -DP的通信過程。其架構(gòu)如圖5所示。

圖5 Nios II系統(tǒng)架構(gòu)

模數(shù)轉(zhuǎn)換器相關(guān)文章:模數(shù)轉(zhuǎn)換器工作原理

溫濕度控制器相關(guān)文章:溫濕度控制器原理 熱電偶相關(guān)文章:熱電偶原理

評論