零基礎學FPGA(十六)testbench很重要,前仿真全過程筆記(下篇)

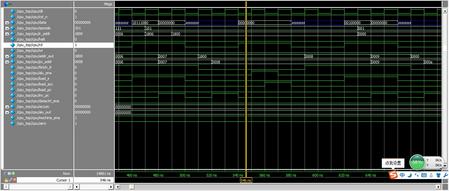

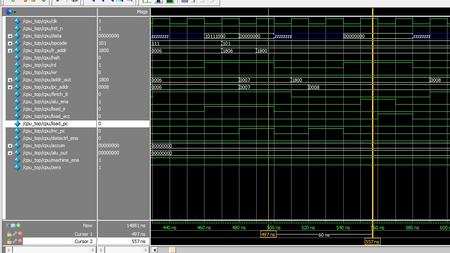

這次讀回的指令碼位101,即LDA,也就是說將后13位地址碼對應的RAM中的數據讀回,送到累加器中,想一下,這時的RAM應該是打開的,而且雙向輸入輸出口的數據總線上應該是來自RAM的8位數據,由于ROM0006地址處的地址碼為1800是13位的,而RAM的地址是9位的,因此實際上我們從RAM中讀回的數據是從RAM的0地址讀回的,即我們之前給RAM寫好的0000_0000,再看一下波形

本文引用地址:http://www.104case.com/article/270619.htm

正如我們所想的一樣,數據總線上是0000_0000,RAM是打開的,地址為1800

就這樣,讀者可以自己再試一下,看看我們的cpu是不是按照我們之前給他的程序運行的,在這里我就不再給大家一一介紹了

雖然波形仿真很直觀,但是看久了就會令人眼花繚亂,尤其是數據很多的時候,我們只能看其中一部分,不能講所有數據看完整,這時候我們單單是用波形來仿真就遠遠不夠了,下面介紹用系統任務仿真的過程

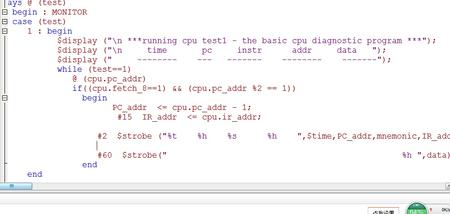

再回到我們的代碼,還記得小墨同學注釋掉了一些代碼吧,我們把那些代碼給加上

我以其中一個過程為例

假設讀回的指令碼位101,即LDA,如果我在fentch_8的高電平期間且在cpu輸出地址為奇數的時候記錄一下此時的時間、指令、地址、目的地址、數據的話就可以不用看波形,讓電腦來幫助我們來分析了,因此作如下處理

這里我延時60ns,是因為第一次記錄的時候數據總線上還沒有數據,只有延時一會才會有數據,即上面那張波形圖右邊那根黃色的線處記錄一下數據,并將其顯示。我們也可以加上一下標注,來幫助我們觀察

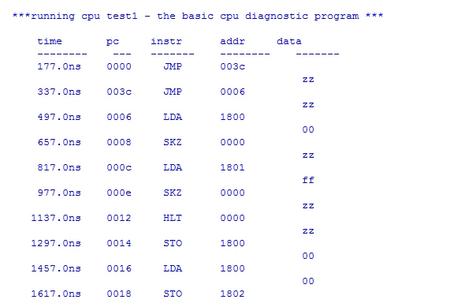

這樣我們再來仿真的時候就不用看波形了,直接打開transcript一欄觀察記錄即可

這樣便可以為我們省下大量的仿真時間

這里小墨同學只做一個事例,其實有很多細節還需要各位讀者自己挖掘,小墨同學在做這個實驗的時候也遇到過不少問題,但是問題總是要解決的,希望各位讀者不要老借助于教程,遇到問題需要自己解決,自己考慮一下應該怎么修改,這樣學到的知識才是最牢固的。

這里小墨同學只做第一個測試,第二第三個測試留給讀者自己完成,我已上傳過代碼,希望廣大讀者多提意見,大家共同進步

純手打~謝謝各位大神支持~

fpga相關文章:fpga是什么

低通濾波器相關文章:低通濾波器原理

評論