多路SDI信號單波長無損光傳輸

接收端RFIFO的功能是從經過碼速調整到30M的數據中還原出27M的數據。其主要實現流程為:采用與發端讀時鐘同步的時鐘為RFIFO的寫時鐘Wrclk,讀時鐘采用本地分出來的符合后端SDI編碼要求的27MHz的時鐘Rclk_27m,由發端傳輸過來的DATA_valid來控制RFIFO的寫使能,從而保證寫入RFIFO的數據都是有效數據,RFIFO的讀使能持續為“1”以保證數據的連續性。整個碼速調整和恢復的信號波形如圖3所示(DATA1為發端輸入的原始數據,DATA2為碼速調整后的同步數據,DATA3為恢復出來的數據。

本文引用地址:http://www.104case.com/article/269823.htm采用這種方法實現起來比較簡單,但是在實際測試時發現:由于SDI_27M_n這個時鐘與Rdclk_30M不同步,從而造成收端進入到RFIFO的數據與RFIFO的讀時鐘Rclk_27M不同步,即RFIFO的讀時鐘與寫時鐘不是同步的,最后必能會造成RFIFO的“寫滿”或者“讀空”,引起SDI信號的誤碼。

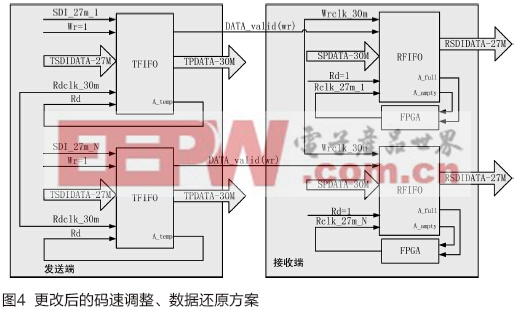

為了解決這個問題,考慮到Rclk_27M與發端的Wrck_27M_N這兩個時鐘雖然是異步的,但是其具體的頻值偏差大約在10PPM左右,將整個系統的碼速調整、數據還原修改成如圖4方案。

如圖4所示,發送端的碼速調整、同步處理方法不變,修改接收端的數據還原部分:原方案中多個RFIFO的讀時鐘是由可編程分出來的同一個27MHz的時鐘,更改后的方案中每個RFIFO的都由FPGA內部PLL分出,該時鐘頻率可以通過FPGA控制在小范圍內動態地變化,具體變化形式由RFIFO的A_full、A_empty的狀態來進行控制:A_full、A_empty分別為RFIFO的快滿或快空標志,在系統啟動時,Rclk_27M_N設置成一個初始值27MHz,隨著設備工作時間的增加,由于讀、寫時鐘的不同步,就會造成RFIFO的快滿會快空,從而引起A_full(快滿)、A_empty(快空)標志置位。當FPGA監測到A_full時,從而判斷當前FIFO的讀時鐘比寫時鐘要慢,FIFO將空,此時通過FPGA控制內部PLL,提高其輸出的Rck_27m_N時鐘的頻率;當FPGA監測到A_empty時,從而判斷當前FIFO的讀時鐘比寫時鐘要快,FIFO將滿,此時通過FPGA控制內部PLL,降低其輸出的Rck_27m_N時鐘的頻率。通過控制RFIFO永遠不會“寫滿”或者“讀空”狀態,確保SDI信號持續有效輸出且不出現誤碼。

3 結論

通過FIFO的“快滿”和“快空”標志控制來控制FPGA內部鎖相環(PLL)的頻率輸出,從而使系統接收端RFIFO的讀時鐘隨FIFO數據深度的變化而實時改變,確保RFIFO不會出現“寫滿”或“讀空”的狀態,解決了原來系統中由于FIFO的問題造成SDI信號誤碼的現象,完成了多路SDI信號的無損光纖傳輸。

目前通過本方案設計的多路SDI單波長光傳輸設備已完成研制,提供給廣電系統多家單位使用,反應效果良好。

參考文獻:

[1]周宇,等. 基于CPLD的異步ASI/SDI信號電復接光傳輸設備的設計[J]. 世界電子元器件,2009,10:58-61

[2]鮑思明.SDI串行數字分量信號格式及檢測方法[J].世界廣播電視,2007,9:43-49

[3]祁超,等.基于FPGA的SD-SDI視頻轉換接口的設計[J].儀表技術與傳感器,2010,10:63-65

[4]李泉,等.用FPGA實現碼速變換[J].電子產品世界,2007,4A:34-36

模擬信號相關文章:什么是模擬信號

dc相關文章:dc是什么

評論