中頻軟件無線電系統的FPGA實現方案

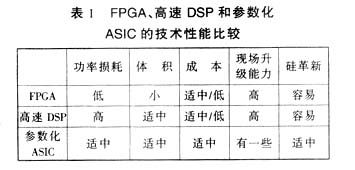

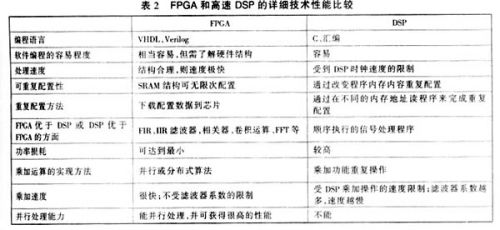

本文采用FPGA來實現中頻軟件無線電。表1和表2所示的比較分析表明,FPGA與參數化ASIC、DSP比較有很多優勢,它不但在功耗、體積、成本方面優于參數化ASIC、DSP,而且處理效率高、現場可編程性能良好。不同于DSP的單流處理方式,FPGA是多流并行處理,這種處理方式使FPGA能完成DSP難以實現的許多功能,如FIR/IIR濾波器、擴頻、跳頻模式。因此,FPGA能很好地體現軟件無線電的靈活性和開放性,很適合在軟件無線電中做高速數字信號處理,是實現中頻軟件無線電的理想選擇。

4.采用FPGA實現中頻軟件無線電系統

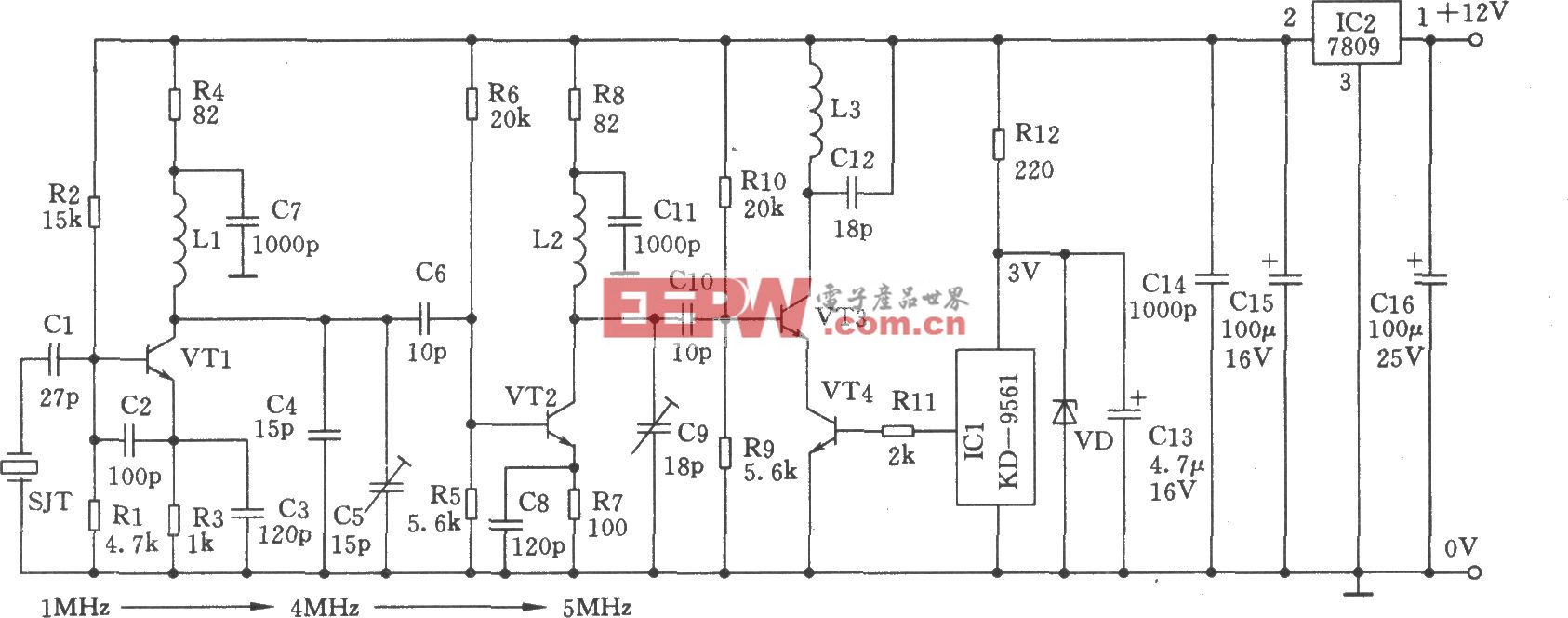

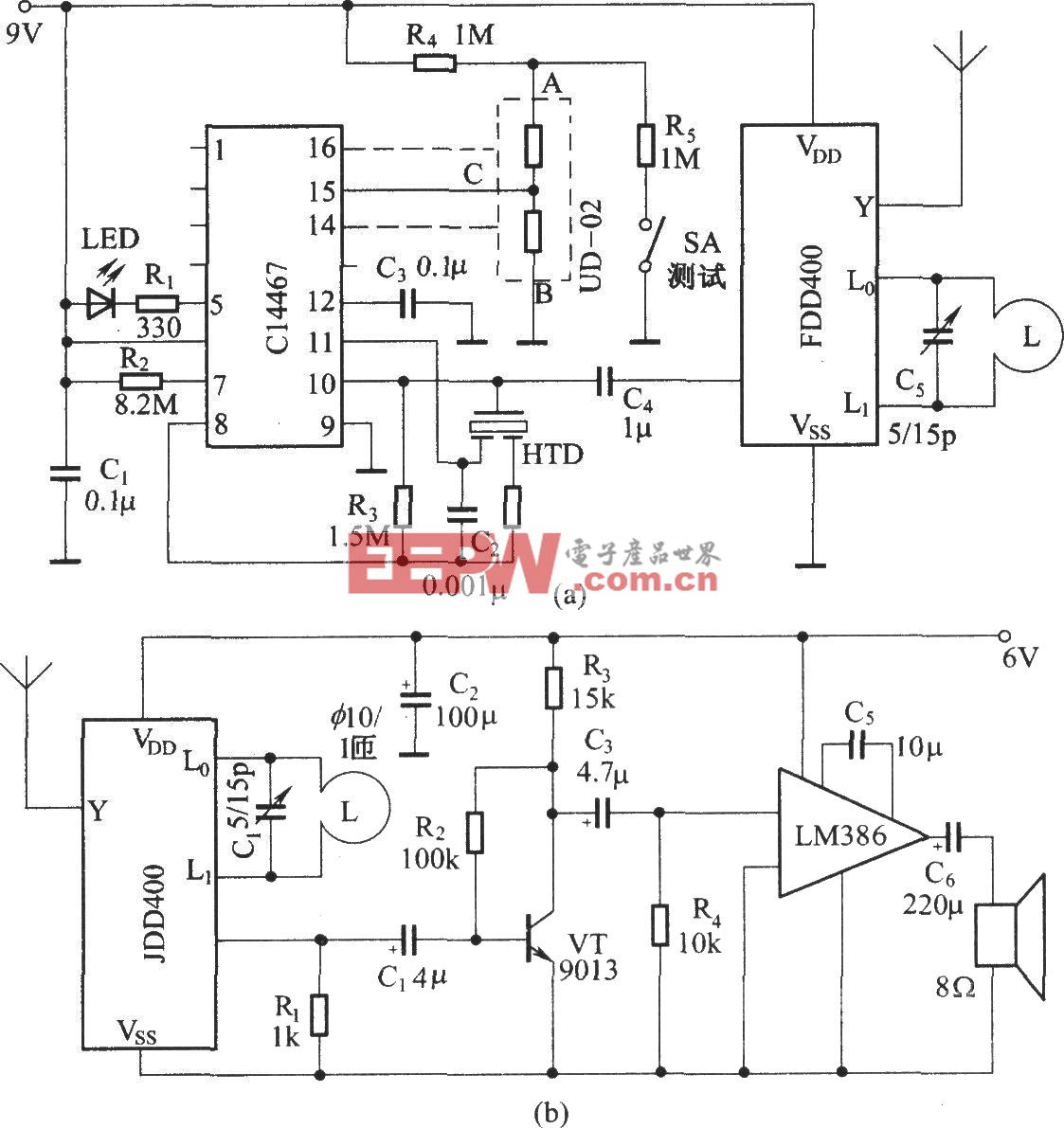

圖3為所實現的中頻軟件無線電系統框圖。系統從IF(中頻)進行A/D和D/A變換。下面就系統的各部分做一介紹。

1 寬帶D/A和A/D轉換器

D/A和A/D轉換器分別把中頻數字信號轉換成模擬信號,中頻模擬信號轉換成數字信號。D/A變換器和A/D變換器的選擇,直接關系到軟件無線電的總體性能。因此,必須根據系統的要求,綜合考慮D/A變換器和A/D變換器的各方面性能,做出選擇。

(1)寬帶D/A轉換器

選用了AD公司的AD9713B,性能指標如下:

1)具有12 bit精度;

2)轉換速率最快為80 MSPS;

3)SFDR(無雜散動態范圍)為70 dBc。

這里,DAC鎖存時鐘為40 MHz。AD9713B后接兩級放大器,將模擬信號放大后輸出。

(2)寬帶A/D轉換器

在軟件無線電中,對ADC的性能要求很高,ADC的選擇比DAC更為重要。選擇ADC時,需要考慮其采樣頻率、帶寬、轉換位數和SFDR。而這幾個性能指標是互為約束的,必須綜合考慮確定。

在此,ADC選用AD公司生產的AD9042。AD9042是高速、高性能、低功耗的單片12位模/數變換器,其性能指標如下:

1)最大采樣速率41 MSPS;

2)SFDR為80 dBc;

3)信噪比為68 dB。

實際使用中,采樣時鐘為40 MHz,AD9042的性能很好。

2 FPGA——數字信號處理模塊

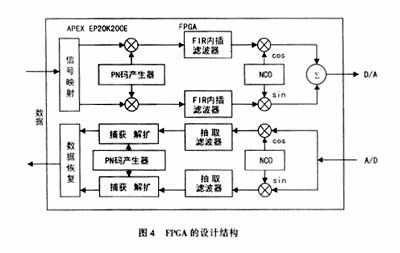

FPGA選用了Altera公司的APEX EP20K200E器件,這個器件為20萬門容量,1.8 V低功耗,具有多種I/O接口和多鐘配置方式的單片系統級集成的可編程邏輯器件。

FPGA主要完成數字上/下變頻、濾波、調制/解調、擴頻/解擴、載波以及PN(偽隨機碼)的同步和跟蹤等功能。

FPGA的設計結構如圖4所示。在此,以DSSS(直接序列擴頻)信號為例說明。發射的設計為,系統將125 kbit/s的數據映射成上下支路各62.5 kbit/s的數據與PN碼產生器輸出的4Mchip/s的PN碼相乘擴頻,然后由14 bit 的FIR濾波器完成內插濾波,濾波器輸出的信號為20 MHz,與NCO相乘上變頻至中頻,并取高12 bit輸出至D/A變換器。接收的設計與發射相對應,A/D變換器輸出的40 MHz的12 bit中頻數字信號與NCO相乘正交下變頻成I、Q兩路信號,這2路信號經抽取濾波變為20 MHz的基帶信號,輸入到解擴電路完成PN碼的捕獲、解擴(用[HJ71mm]匹配濾波器相關器實現)以及信號相關后的功率檢測,解擴后的信號和檢測到的功率信號輸入到碼跟蹤電路完成碼元跟蹤,最后完成解碼,恢復數據。完成這些功能,所占的FPGA資源為:7142個LE(邏輯單元),16896 ESB(嵌入式邏輯塊) bits。

dc相關文章:dc是什么

fpga相關文章:fpga是什么

評論