基于FPGA的軟件無線電平臺設計

1.4 CPU控制單元

本文引用地址:http://www.104case.com/article/269660.htmVirtex-4 FX系列FPGA集成了運行速度高達450 MHz的雙32位嵌入式PowerPC,每個處理器可提供超過700 DhrySTone MIPS的性能,是普通FPGA中處理器性能的三倍。兩個完全集成的UNH認證的10/100/1000 Ethernet MAC進一步提升了Virtex-4 FX處理平臺的性能,從而提高了FPGA資源的可用性。本系統(tǒng)以PowerPC作為該系統(tǒng)的指令處理和控制單元,可以避免純硬件設計復雜,通用性差和不容 易協(xié)調控制的缺點。PowerPC是本系統(tǒng)SoPC架構的核心組成部分,擔負算法實現(xiàn)和中央控制兩部分任務。Virtex-4 FX內(nèi)部有大量乘法器可供調用,能夠充分滿足各種數(shù)字信號處理要求;

PowerPC與前文提到用Verilog-HDL 設計的DSP模塊連接,使整個系統(tǒng)具有實時動態(tài)信號的處理能力。PowerPC作為控制器的狀態(tài)流程如圖3所示。

2 FSK設計實例及仿真結果

在現(xiàn)代通信中,調制器的載波信號幾乎都是正弦信號,數(shù)字基帶信號通過調制器改變正弦載波頻率,產(chǎn)生移頻鍵控(FSK)信號。FSK時域表達式為

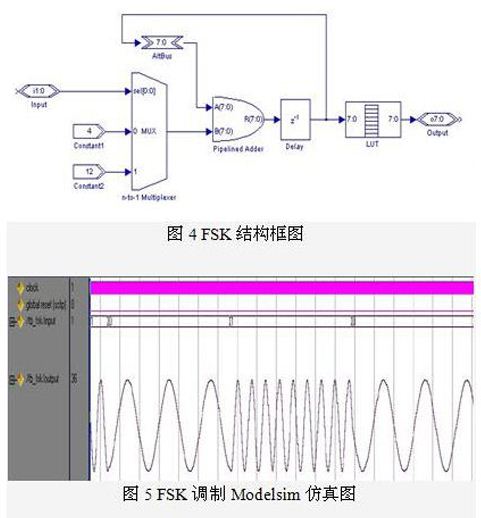

用本系統(tǒng)實現(xiàn)FSK調制結構框圖如圖4所示,用Verilog-HDL語言編寫實現(xiàn)的FSK調制模塊,相對于傳統(tǒng)軟件無線電的實現(xiàn)方式,省去了讀取指令周期的時間,總運算時間縮短了一半。FSK調制的ModelSim波形仿真結果如圖5所示。

3 結論

改進的基于FPGA的嵌入式軟件無 線電系統(tǒng),可更好地滿足通信、雷達、數(shù)字電視等高科技領域對信號處理實時性的要求。運用軟件無線電和SoPC技術,極大的提高了系統(tǒng)動態(tài)實時信號的處理能 力。在節(jié)約資源方面,以節(jié)省芯片數(shù)量計算,該系統(tǒng)相對于目前常規(guī)系統(tǒng),節(jié)省功耗和體積可達30%以上。40MHZ時鐘頻率, 12bit精度,80dB無寄生動態(tài)范圍,該系統(tǒng)可以應用于Cellular / PCS基站,多通道多模式接收機,GPS抗干擾接收機,相控陣接收機,頻譜分析,3G無線通信等領域。

評論