不同的verilog代碼風格看RTL視圖之一

剛開始玩CPLD/FPGA開發(fā)板的時候使用的一塊基于EPM240T100的板子,alter的這塊芯片雖說功耗小體積小,但是資源還是很小的,你寫點稍微復雜的程序,如果不注意coding style,很容易就溢出了。當時做一個三位數(shù)的解碼基本就讓我苦死了,對coding style的重要性也算是有一個比較深刻的認識了。

本文引用地址:http://www.104case.com/article/268450.htm后來因為一直在玩xilinx的spartan3 xc3s400,這塊芯片資源相當豐富,甚至于我在它里面緩存了一幀640*480*3/8BYTE的數(shù)據(jù)都沒有問題(VGA顯示用)。而最近接觸EPM7128,它的資源似乎也不豐富,我寫著寫著有時不注意就無法布線了。由此可見coding style對設計的重要性,尤其是在資源緊張或者速度要求較高的設計中。我個人對前者的體會深一些,高速的設計沒有涉及過,只是明白一些用流水線提高速度的方法。

可以步入正題了,先拿一段簡單的代碼開始吧。我先提一點,這回我用的是quartus II 7.0進行測試,其它的EDA工具綜合出來的RTL視圖可能會不一樣,所以僅作為在quartus II 7.0環(huán)境下的一些參考吧。不過思路是一樣的,可以借鑒的。

Ex1:

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0);

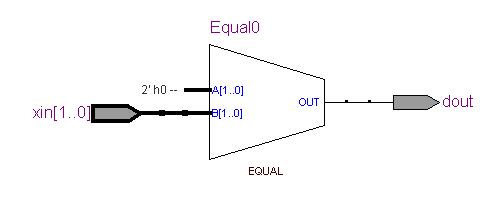

代碼很簡單,就是當xin==2’b0時dout=1,否則dout=0。上面這段程序的RTL視圖如下:

其實就是一個比較器,如果xin=2’h0,那么輸出OUT就為1。和設想一樣。

下面是我在參考一些別人的代碼的時候看到別人一種常見的寫法,它是用了?語句。

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0) ? 1'b1:1'b0;

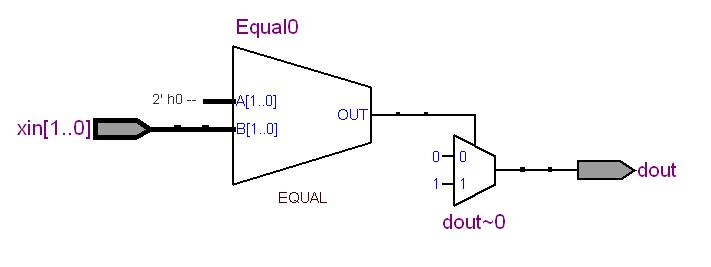

RTL如下:

是不是發(fā)現(xiàn)多了以一個選擇器(可能不叫選擇器吧,但是你明白意思就可以),這樣平白無故的就多耗用了一點資源,剛開始的時候我也是傻乎乎的跟著別人用這種寫法,但是看到RTL視圖后我就不這么干了,既然前者一樣可以得到預期結果,為什么我還要畫蛇添足多一個選擇器呢。所以,推薦使用前者。資源的節(jié)約是潛移默化的~_~

(先說一點吧,其它的待我想起或者是感悟到了再提吧,以上也完全是我的個人愚見,如有不妥之處歡迎拍磚~_~)

評論