基于SoPC的FIR濾波器設計與實現

2.3 生成VHDL語言

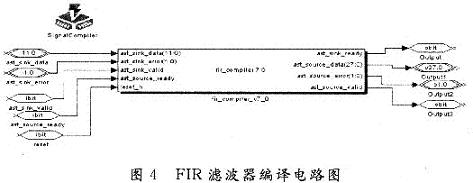

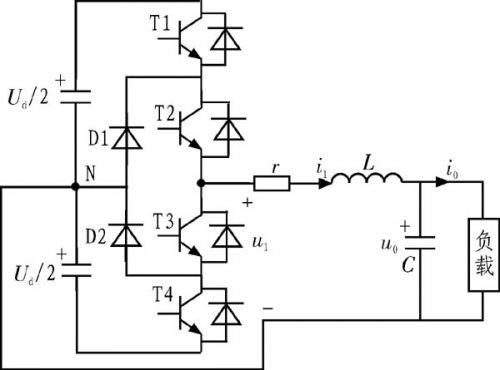

本文引用地址:http://www.104case.com/article/267759.htm完成FIR濾波器核配置后,便可得到設計好的濾波器,加入輸入/輸出信號,形成如圖4所示電路。點擊SignalCompiler,再選擇Anal-yze,選擇Sigle step compilation中的Convert MDL to VHDL,就可以生成對應的VHDL語言。

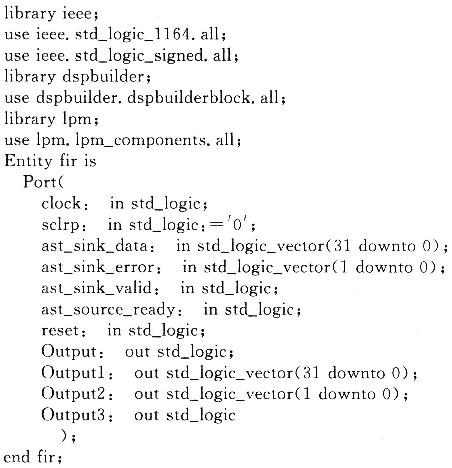

在QuartusⅡ中打開編譯后生成的fir.qpf工程文件,可以得到濾波器的VHDL語言,其部分代碼如下:

編譯成功后,可以將其轉換成元件。

2.4 系統功能仿真

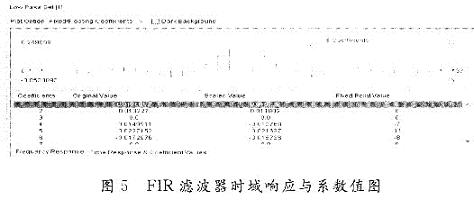

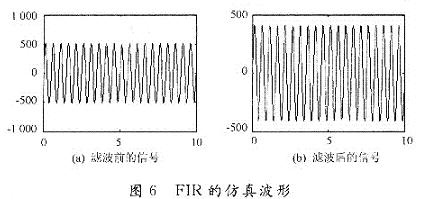

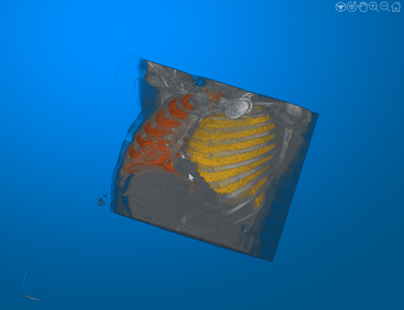

在Matlab中,建立M文件,運用前面設置好參數所生成的FIR濾波器,打開FIR濾波器時域響應與系數值(time response & coefficeient vahles)。得到該濾波器的時域響應和系數值如圖5所示,由該系數表確定濾波器,并進行算法級仿真,得到如圖6所示的波形。

圖6(a)為濾波前信號,圖6(b)為濾波后信號。從仿真波形可以看出,經過FIR濾波器之后,高次諧波信號被很好地濾除了,達到了預定的設計目標。

3 基本FPGA片上系統的功能測試

設計目標器件選用美國Altera公司Cyclone系列FPGA器件中的EP3C25E144C8N芯片,通過開發工具QuartusⅡ對各個模塊的VHDL源程序及頂層電路進行編譯、邏輯綜合、電路的糾錯、驗證、自動布局布線及仿真等各種測試,最終將設計編譯的數據下載到芯片中,同時與單片機AT89C51結合,進一步進行數據的快速處理和控制,實現鍵盤可設置參數及LCD顯示。經實際電路測試驗證,達到了設計的要求。

4 結語

這種基于SoPC數字濾波器的設計與實現,不僅利用Matlab中的Simulink與Alterl DSP Builder工具確定FIR濾波器系數,不用編程,只需簡單的設置,而且通過VHDL層次化設計方法,同時使FPGA與單片機相結合,采用C51及VHDL語言模塊化設計思想進行優化編程,進一步完善了數據的快速處理和有效控制,提高了設計的靈活性、可靠性,也增強了系統功能的可擴展性。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

高通濾波器相關文章:高通濾波器原理 數字濾波器相關文章:數字濾波器原理

評論