基于XC2V1000型FPGA的FIR抽取濾波器的設計

4.1.1控制器(fir_controller)

本文引用地址:http://www.104case.com/article/267749.htm控制器是抽取濾波器的核心模塊,有2種功能:接收輸入數據,向其他模塊發送數據和控制信號。它根據加法器、乘法器和累加器的時序特性,規律地向加法器發送抽頭數據,向乘法器發送系數,向累加器發送控制信號,讓加法器、乘法器和累加器每個時鐘都完成指定的任務,從而實現流水線操作。控制器用YHDL語言描述,用寄存器存放抽頭和系數。

4.1.2加法器(adder18)

加法器的輸入和輸出都是18bits,用VHDL語言描述實現。它有2個工作時鐘的延遲,在輸入數據準備好的情況下,第一個時鐘得出相加結果,第二個時鐘把相加結果鎖存輸出。

4.1.3乘法器(multl8)

乘法器是18bits輸入和36bits輸出,用庫元件MULT18X18S和36bits鎖存器實現。MULT18Xl8S是XC2V1000自帶的18×18bits乘法器,單個時鐘就可完成乘法運算;36bits鎖存器工作于時鐘的上升沿,用VHDL語言描述。乘法器(mult18)也有2個工作時鐘的延時,在輸入數據準備好的情況下,第一個時鐘得出相乘結果,第二個時鐘把相乘結果鎖存輸出。加法器和乘法器采用鎖存輸出的結構,雖然增加了1個工作時鐘的延遲,但有利于抽取濾波器穩定的工作,提高可靠性。

4.1.4累加器(acc36)

36bits累加器用于累加乘法器的輸出,得出濾波結果。它有1個控制端口clr,當clr為高電平時,輸出前一輪累加結果,并初始化開始新一輪累加;當clr為低電平時.進行累加運算。累加器用VHDL語言描述。

4.1.5數據截位器(signal_36-18)

數據截位器用VHDL語言描述,用于把累加器的36位輸出進行取舍處理,一般截掉數據低位部分,保留數據高位。為了對抽取濾波器進行功能仿真,這里截掉數據高18位,保留數據低18位。

4.2 工作過程及功能仿真

加法器、乘法器和累加器在控制器的作用下每個時鐘都要完成指定的任務,從而形成流水線操作,實現抽取濾波。

下面以抽取濾波器完成1次抽取濾波的全過程為例,說明抽取濾波器的工作過程。假設時鐘1、時鐘2、時鐘3和時鐘4控制器已接收了數據x(n-3)、x(n-2)、x(n-1)和x(n),那么,

時鐘5:控制器向加法器發送數據x(n)和x(n-3);

時鐘6:加法器進行。x(n)+x(n-3)運算;控制器向加法器發送數據x(n-1)和x(n-2);

時鐘7:加法器進行x(n-1)+x(n-2)運算,輸出x (n)+x(n-3)運算結果。控制器向乘法器發送系數h(0);

時鐘8:加法器輸出x(n-1)+x(n-2)運算結果,乘法器進行h(0)[x(n)+x(n-3)]運算,控制器向乘法器發送系數h(1) ;

時鐘9:乘法器進行h(1)[x(n-1)+x(n-2)]運算,輸出h(0)[x(n)+x(n-3)1運算結果。控制器向累加器發送控制信號(clr為高電平);

時鐘10:乘法器輸出h(1)[x(n-1)+x(n-2)]運算結果。累加器初始化開始累加操作。控制器向累加器發送控制信號(clr為低電平);

時鐘11:累加器進行累加運算h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]。控制器向累加器發送控制信號(clr為高電平),控制器輸出濾波數據有效信號(valid為高電平);

時鐘12:累加器輸出h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]累加結果,并初始化開始新一輪累加操作。控制器輸出濾波數據無效信號(valid為低電平);

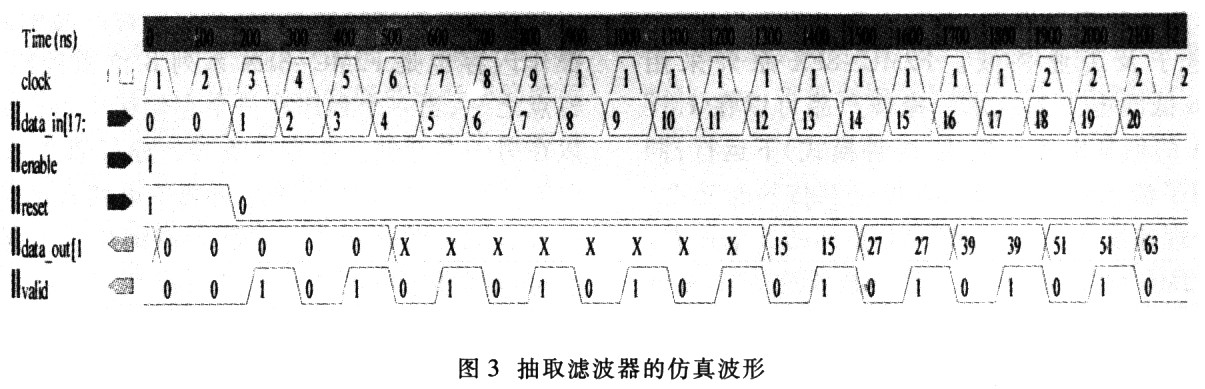

以上就是抽取濾波器完成1次抽取濾波的全過程。可見,從數據x(n)輸入到濾波結果y(n)輸出需要8個工作時鐘。如果控制器不停地向加法器、乘法器和加法器發送抽頭、系數和控制信號,就會形成流水線操作,那么每2個時鐘,抽取濾波器就會輸出1個濾波結果。圖3是抽取濾波器的仿真波形圖,其中在控制器中設置系數h(0)=1和h(1)=2。

4.3注意事項

2個n位二進制數相加,其和至少需要n+l位二進制數才能正確表示。本設計中的加法器輸入輸出都是18位,為了防止加法器溢出,應確保18位輸入數據x(n)的最高2位相同(都是符號位)。

為了實現抽取濾波器的多級串聯結構,應統一輸入數據有效信號enable和輸出數據有效信號valid的時序要求。本設計規定控制器在累加器輸出濾波結果數后下1個時鐘送出濾波結果有效信號,時寬為1個工作時鐘周期。

5 設計特點

采用此設計結構實現抽取濾波器具有以下3個特點:

(1)節省片內資源和提高資源使用效率

Xilinx公司為了方便用戶設計濾波器,在IP核中集成了通用數字濾波器的設計,但利用IP核生成的數字濾波器往往不能針對實際情況合理地利用片內資源,造成資源浪費。本設計中采用了流水線結構,所有功能模塊都滿負荷工作,沒有空閑等待時鐘,從而節省了片內資源,提高了資源使用率。

(2)可以實現抽取濾波器多級結構

針對抽取濾波器的輸出特性,可以采取相同的設計方法再設計一級抽取濾波器,對前一級輸出的數據再次抽取濾波,從而實現多級抽取濾波器結構。

(3)設計靈活且擴展性強

用寄存器存放抽頭和系數適用于濾波器階數較少的情況,如果需要用上百階的抽取濾波,最好用片內:RAM存放抽頭和系數,這時只要稍加改動控制器的邏輯設計既可實現。在此基礎上,還可實現可編程抽取濾波器。

6 結束語

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。用該方法設計出的抽取濾波器靈活性強、資源利用率高,能廣泛應用于數字接收領域。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論