基于FPGA 的FIR 數字濾波器設計方案

在QuartusⅡ環境下,數字濾波器的內部邏輯經過編譯適配之后,以。sof文件的形式直接加載到FPGA中。

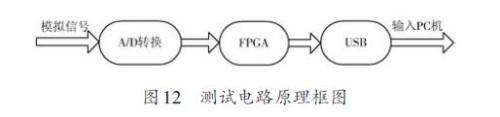

本文引用地址:http://www.104case.com/article/267746.htm進行實時測試的電路是應用FPGA和USB的數據采集電路,如圖12所示。

測試時把信號發生器設置好的輸入信號輸入到A/D,采樣得到的數據經過FPGA,再通過USB與PC機相連,應用QuartusⅡ中的SignalTapⅡ工具進行實時檢測,結果如圖13所示,其中,上面的波形為輸入波形,頻率為200 Hz,下面的波形為輸出波形,由于200 Hz在低通的帶通內,所以兩者的波形相差不大。當輸入波形為頻率533 Hz時,由于是在截頻點,其輸出波形的幅值約為輸入波形幅值的71%,如圖13和14所示。

5結束

FIR數字濾波器在數字信號處理領域有著廣泛的使用,本文通過仿真和實時驗證兩種方式實現了一種基于FPGA和DSP Builder的FIR數字濾波器。先根據FIR濾波器的基本原理和結構框圖搭建了濾波器的模型,再根據濾波器的性能指標通過FDATool工具對其進行設計,并通過系統級仿真和ModelSim功能仿真進行了簡要的可行性分析,最后通過QuartusⅡ軟件對FIR數字濾波器進行實時驗證,表明本方案所設計的FIR濾波器功能正確,性能良好。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論